# S3 Family 8-Bit Microcontrollers

# S3F94C8/S3F94C4

# **Product Specification**

PS031503-0115

PRELIMINARY

Copyright ©2015 Zilog<sup>®</sup>, Inc. All rights reserved. www.zilog.com

ii

## Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2015 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

S3 and Z8 are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

iii

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Description                                                                                                                                               | Page |

|-------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Jan<br>2015 | 03                | Updated the Third Parties for Development Tools section.                                                                                                  | 17-9 |

| May<br>2014 | 02                | Corrected R value in Figure 8-2 and following note to $40K\Omega$ ; entire document updated to include front matter, PDF bookmarks for easier navigation. | 8-3  |

| Aug<br>2013 | 01                | Original Zilog issue.                                                                                                                                     | All  |

# **Chip Handling Guide**

#### **Precaution Against Electrostatic Discharge**

When handling semiconductor devices, be sure that the environment is protected against static electricity.

- 1. Operators should wear anti-static clothing and use earth band.

- 2. All objects that come in direct contact with devices should be made of materials that do not produce static electricity that would cause damage.

- 3. Equipment and work table must be earthed.

- 4. Ionizer is recommended to remove electron charge.

#### Contamination

Be sure to use semiconductor products in the environment that may not be exposed to dust or dirt adhesion.

#### Temperature/Humidity

Semiconductor devices are sensitive to environment temperature and humidity. High temperature or humidity may deteriorate semiconductor device's characteristics. Therefore avoid storage or use in such conditions.

#### **Mechanical Shock**

Care should be exercised not to apply excessive mechanical shock or force on semiconductor device.

#### Chemical

Do not expose semiconductor device to chemical because reaction to chemical may cause deterioration of device characteristics.

#### **Light Protection**

In case of non-EMC (Epoxy Molding Compound) package, do not expose semiconductor IC to strong light. It may cause device's malfunction. (But, some special products which utilize the light or have security function are excepted from this guide)

#### Radioactive, Cosmic and X-Ray

Semiconductor devices can be influenced by radioactive, cosmic ray or X-ray. Radioactive, cosmic and X-ray may cause soft error during device operation. Therefore semiconductor devices must be shielded under environment that may be exposed to radioactive, cosmic ray or X-ray.

#### Electromagnetic Susceptibility (EMS)

Note that semiconductor device's characteristics may be affected by strong electromagnetic wave or magnetic field during operation under insufficient PCB circuit design for EMS.

# **Table of Contents**

| Chip H  | landling Guide                                                                                                                                                    | iv   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| List of | Figures                                                                                                                                                           | x    |

| List of | Tables                                                                                                                                                            | xiii |

| 1 Prod  | luct Overview                                                                                                                                                     |      |

| 1.1     | SAM88RCRI Microcontrollers                                                                                                                                        |      |

| 1.2     | S3F94C8/S3F94C4 Microcontroller                                                                                                                                   |      |

| 1.3     | Features                                                                                                                                                          |      |

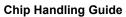

| 1.4     | Block Diagram                                                                                                                                                     |      |

| 1.5     | Pin Assignments                                                                                                                                                   |      |

| 1.6     | Pin Descriptions                                                                                                                                                  |      |

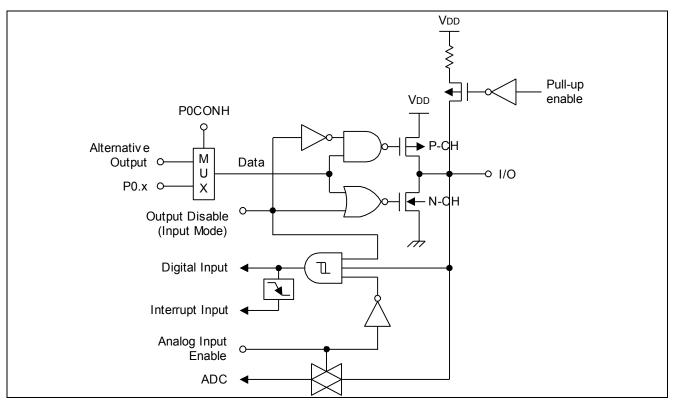

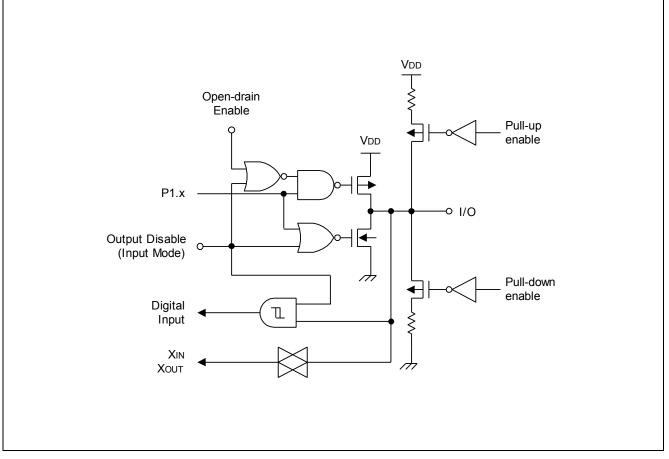

| 1.7     | Pin Circuits                                                                                                                                                      | 1-7  |

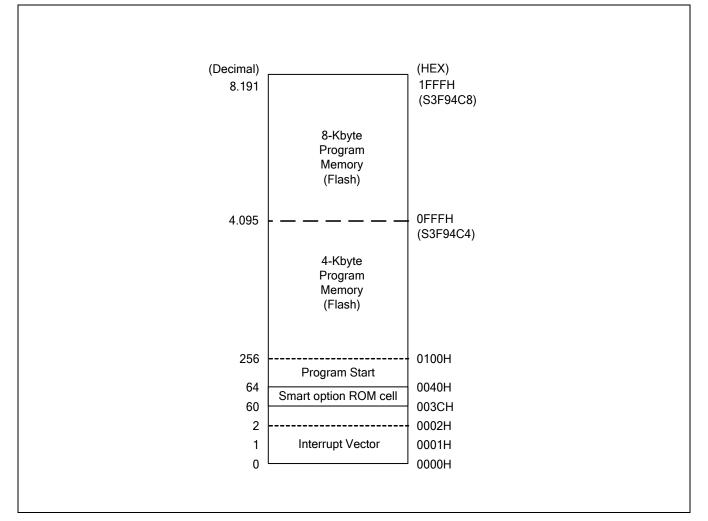

| 2 Addr  | ess Spaces                                                                                                                                                        | 2-1  |

| 2.1     | Overview                                                                                                                                                          | 2-1  |

| 2.2     | Program Memory (ROM)                                                                                                                                              |      |

|         | 2.2.1 Normal Operating Mode                                                                                                                                       |      |

| 2.3     | Smart Option                                                                                                                                                      |      |

| 2.4     | Register Architecture                                                                                                                                             |      |

| 2.5     | Common Working Register Area (C0H–CFH)                                                                                                                            |      |

| 2.6     | System Stack                                                                                                                                                      | 2-8  |

|         | 2.6.1 Stack Operations                                                                                                                                            |      |

|         | 2.6.2 Stack Pointer (SP)                                                                                                                                          |      |

| 3 Addr  | essing Modes                                                                                                                                                      | 3-1  |

| 3.1     | Overview                                                                                                                                                          |      |

| 3.2     | Register Addressing Mode (R)                                                                                                                                      |      |

| 3.3     | Indirect Register Addressing Mode (IR)                                                                                                                            |      |

| 3.4     | Indexed Addressing Mode (X)                                                                                                                                       |      |

| 3.5     | Direct Address Mode (DA)                                                                                                                                          |      |

| 3.6     | Relative Address Mode (RA)                                                                                                                                        |      |

| 3.7     | Immediate Mode (IM)                                                                                                                                               | 3-12 |

| 4 Cont  | trol Registers                                                                                                                                                    |      |

| 4.1     | Overview                                                                                                                                                          |      |

|         | 4.1.1 ADCON — A/D Converter Control Register (F7H)                                                                                                                |      |

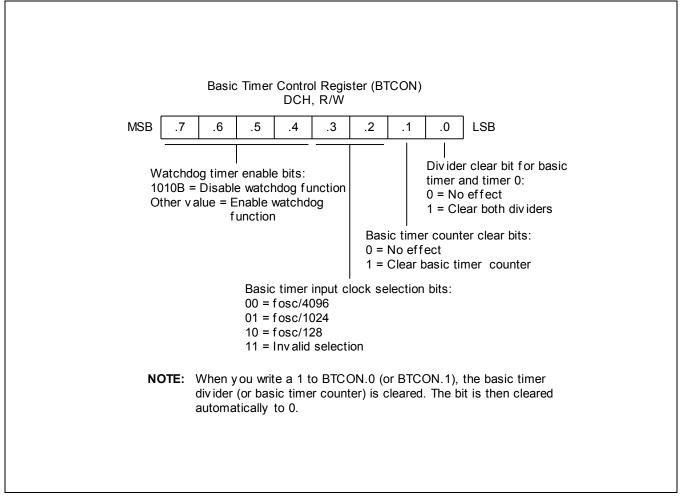

|         | 4.1.2 BTCON — Basic Timer Control Register (DCH)                                                                                                                  |      |

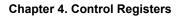

|         | 4.1.3 CLKCON — Clock Control Register (D4H)<br>4.1.4 FLAGS — System Flags Register (D5H)                                                                          |      |

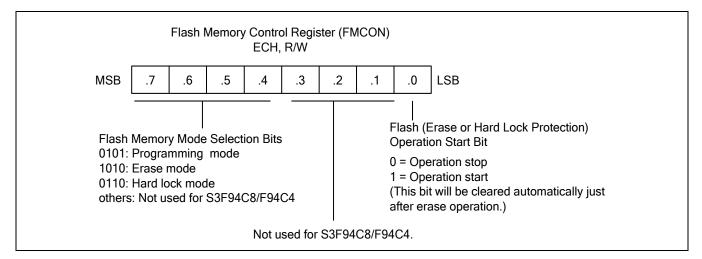

|         | 4.1.5 FMCON — Flash Memory Control Register (ECH)                                                                                                                 |      |

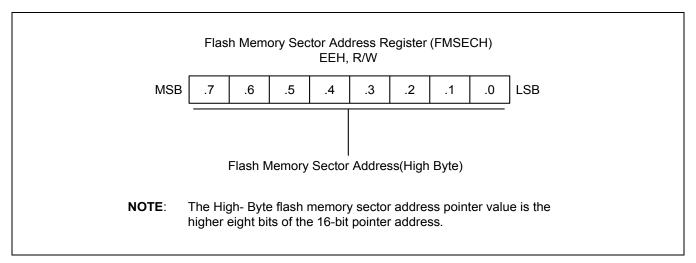

|         | 4.1.6 FMSECH — Flash Memory Sector Address High Byte Register (EEH)                                                                                               |      |

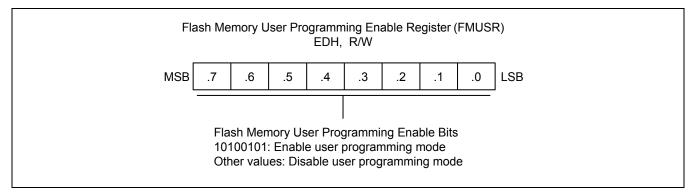

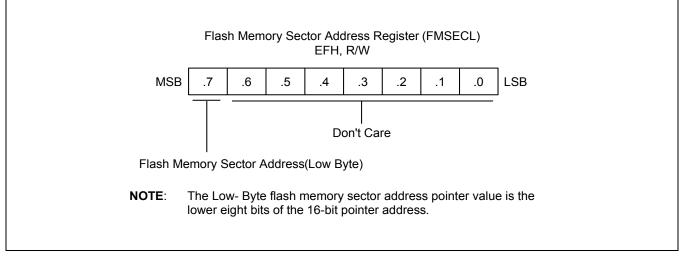

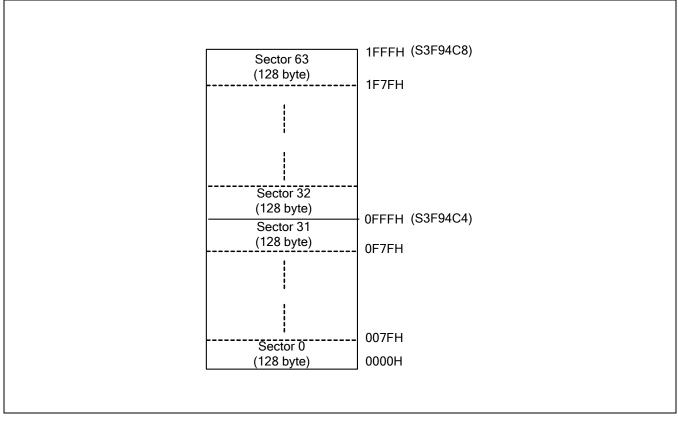

|         | <ul> <li>4.1.7 FMSECL — Flash Memory Sector Address Low Byte Register (EFH)</li> <li>4.1.8 FMUSR — Flash Memory User Programming Enable Register (EDH)</li> </ul> |      |

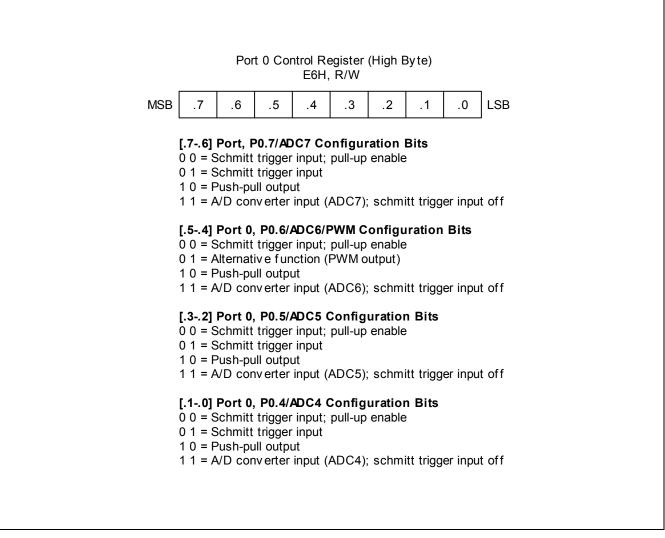

|         | 4.1.9 POCONH — Port 0 Control High Byte Register (E6H)                                                                                                            |      |

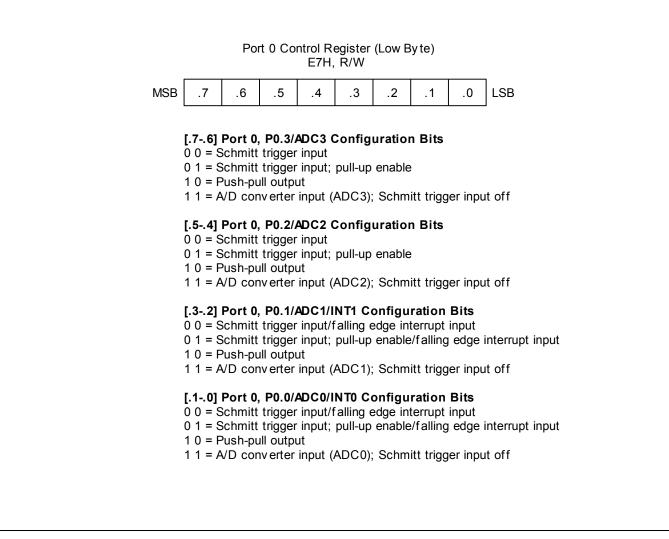

|         | 4.1.10 P0CONL — Port 0 Control Low Byte Register (E7H)                                                                                                            |      |

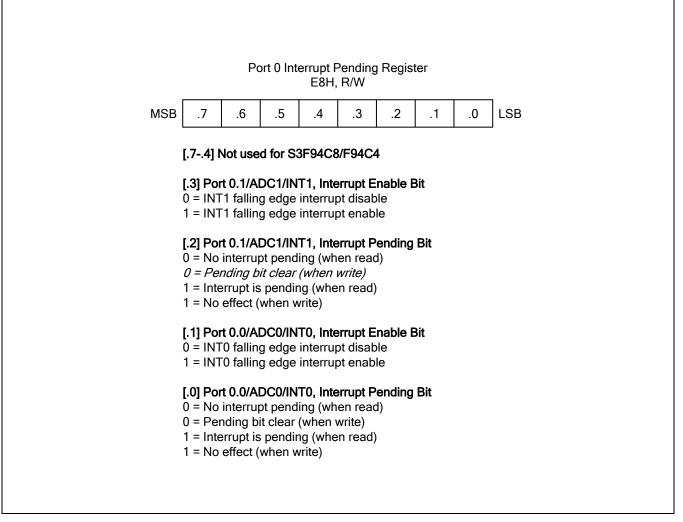

|         | 4.1.11 P0PND — Port 0 Interrupt Pending Register (E8H)                                                                                                            |      |

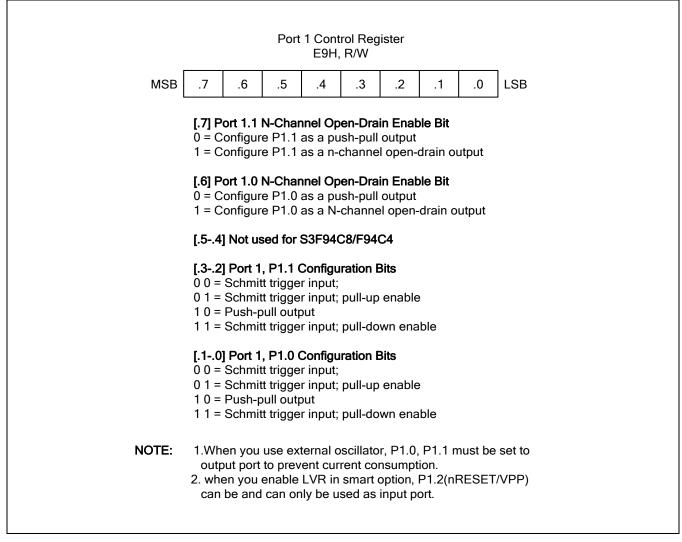

|         | 4.1.12 P1CON — Port 1 Control Register (E9H)            | 4-15 |

|---------|---------------------------------------------------------|------|

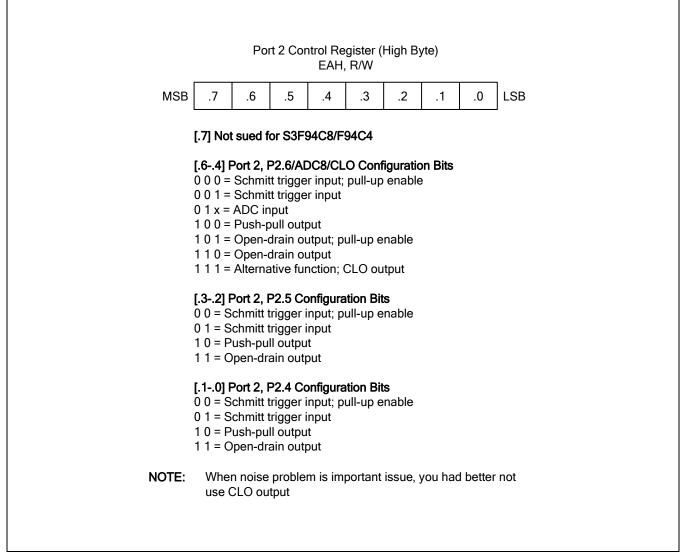

|         | 4.1.13 P2CONH — Port 2 Control High Byte Register (EAH) |      |

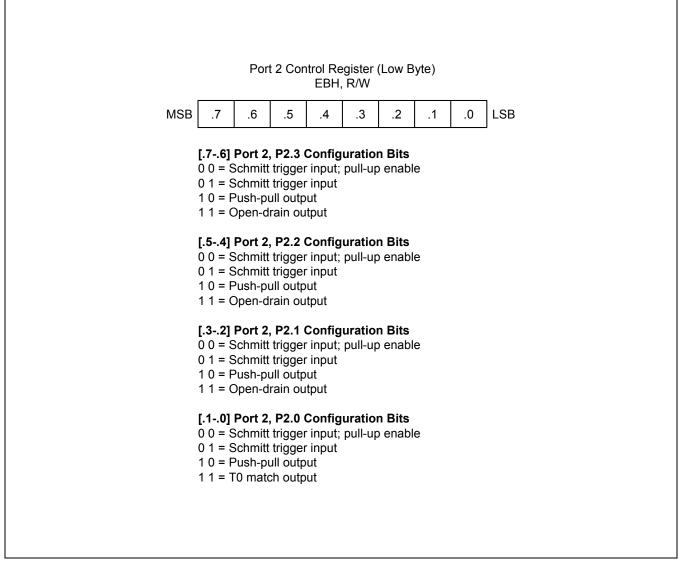

|         | 4.1.14 P2CONL — Port 2 Control Low Byte Register (ÈBH)  |      |

|         | 4.1.15 PWMCON — PWM Control Register (F3H)              |      |

|         | 4.1.16 PWMEX — PWM Extension Register (F1H)             |      |

|         | 4.1.17 STOPCON — Stop Mode Control Register (E4H)       | 4-21 |

|         | 4.1.18 SYM — System Mode Register (DFH)                 | 4-22 |

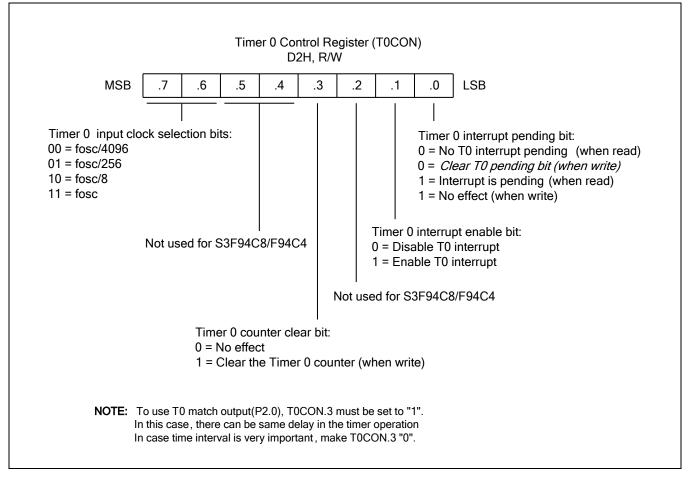

|         | 4.1.19 T0CON — Timer 0 Control Register (D2H)           | 4-23 |

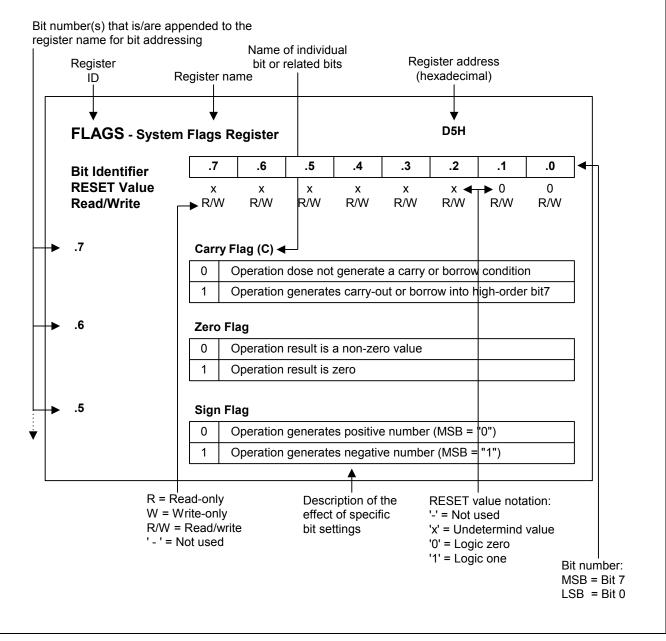

| 5 Inter | rupt Structure                                          | 5_1  |

|         | •                                                       |      |

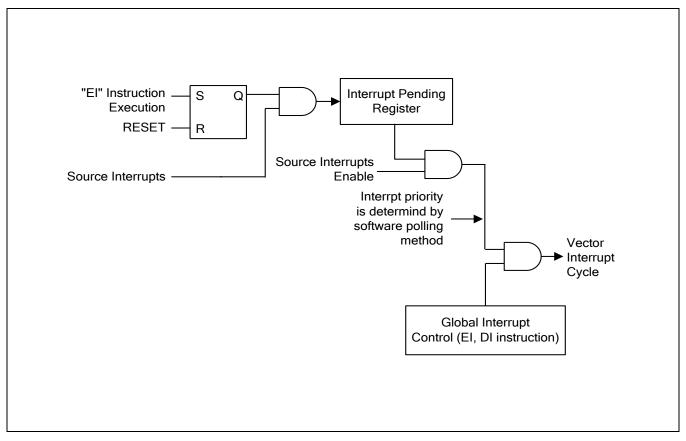

|         | Overview                                                |      |

| 5.2     | Interrupt Processing Control Points                     |      |

| 5.3     | Enable/Disable Interrupt Instructions (EI, DI)          |      |

| 5.4     | Interrupt Pending Function Types                        |      |

| 5.5     | Interrupt Priority                                      |      |

| 5.6     | Interrupt Source Service Sequence                       | 5-3  |

| 5.7     | Interrupt Service Routines                              | 5-3  |

| 5.8     | Generating interrupt Vector Addresses                   | 5-3  |

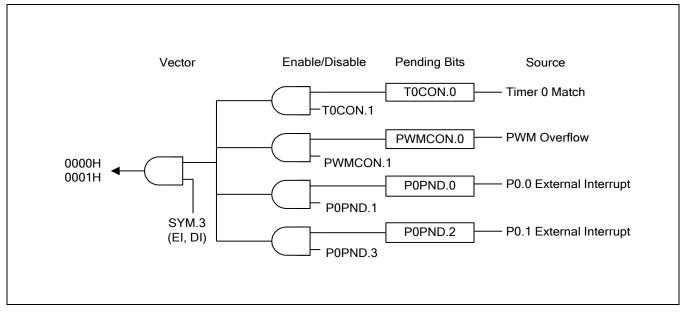

| 5.9     | S3F94C8/S3F94C4 Interrupt Structure                     | 5-4  |

| 5.10    | Peripheral Interrupt Control Registers                  | 5-5  |

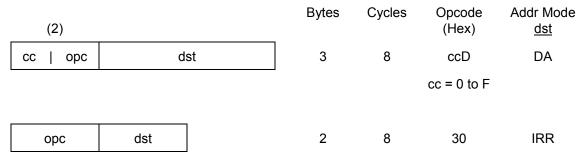

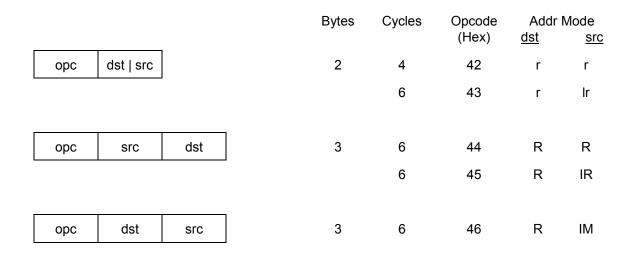

| 6 Instr | uction Set                                              | 6-1  |

|         | Overview                                                |      |

|         | Register Addressing                                     |      |

|         | Addressing Modes                                        |      |

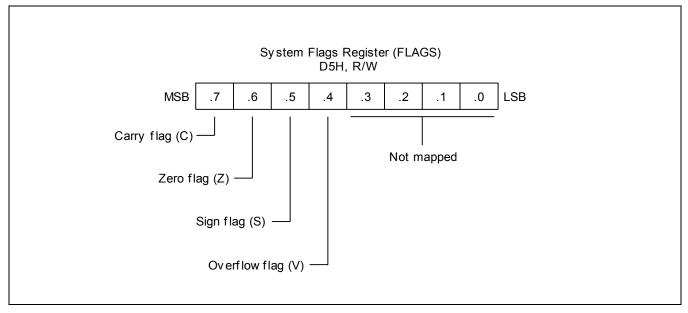

| 6.4     | Flags Register                                          |      |

| 6.5     | Flag Descriptions                                       |      |

|         | 6.5.1 Overflow Flag (FLAGS.4, V)                        |      |

|         | 6.5.2 Sign Flag (FLAGS.5, S)                            |      |

|         | 6.5.3 Zero Flag (FLAGS.6, Z)                            |      |

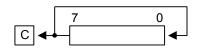

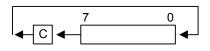

|         | 6.5.4 Carry Flag (FLAGS.7, C)                           |      |

| 6.6     | Instruction Set Notation                                |      |

| 6.7     | Condition Codes                                         |      |

| 6.8     | Instruction Descriptions                                |      |

| 0.0     | 6.8.1 ADC — Add with Carry                              |      |

|         | 6.8.2 ADD — Add                                         |      |

|         | 6.8.3 AND — Logical AND                                 |      |

|         | 6.8.4 CALL — Call Procedure                             |      |

|         | 6.8.5 CCF — Complement Carry Flag                       |      |

|         | 6.8.6 CLR — Clear                                       |      |

|         | 6.8.7 COM — Complement.                                 |      |

|         | 6.8.8 CP — Compare                                      |      |

|         | 6.8.9 DEC — Decrement                                   |      |

|         | 6.8.10 DI — Disable Interrupts                          |      |

|         | 6.8.11 El — Enable Interrupts                           |      |

|         | 6.8.12 IDLE — Idle Operation                            |      |

|         | 6.8.13 INC — Increment                                  |      |

|         | 6.8.14 IRET — Interrupt Return                          |      |

|         | 6.8.15 JP — Jump                                        |      |

|         | 6.8.16 JR — Jump Relative                               |      |

|         | 6.8.17 LD — Load                                        |      |

|         | 6.8.18 LD — Load                                        |      |

|         | 6.8.19 LDC/LDE — Load Memory                            | 6-29 |

|       | 6.8.20 LDC/LDE — Load Memory                                              |      |

|-------|---------------------------------------------------------------------------|------|

|       | 6.8.21 LDCD/LDED — Load Memory and Decrement                              |      |

|       | 6.8.22 LDCI/LDEI — Load Memory and Increment<br>6.8.23 NOP — No Operation |      |

|       | 6.8.24 OR — Logical OR                                                    |      |

|       | 6.8.25 POP — Pop From Stack                                               |      |

|       | 6.8.26 PUSH — Push To Stack                                               |      |

|       | 6.8.27 RCF — Reset Carry Flag                                             |      |

|       | 6.8.28 RET — Return                                                       |      |

|       | 6.8.29 RL — Rotate Left                                                   |      |

|       | 6.8.30 RLC — Rotate Left Through Carry<br>6.8.31 RR — Rotate Right        |      |

|       | 6.8.32 RRC — Rotate Right Through Carry                                   |      |

|       | 6.8.33 SBC — Subtract With Carry                                          |      |

|       | 6.8.34 SCF — Set Carry Flag                                               |      |

|       | 6.8.35 SRA — Shift Right Arithmetic                                       |      |

|       | 6.8.36 STOP — Stop Operation                                              |      |

|       | 6.8.37 SUB — Subtract                                                     |      |

|       | 6.8.38 TCM — Test Complement Under Mask                                   |      |

|       | 6.8.39 TM — Test Under Mask<br>6.8.40 XOR — Logical Exclusive OR          |      |

|       |                                                                           |      |

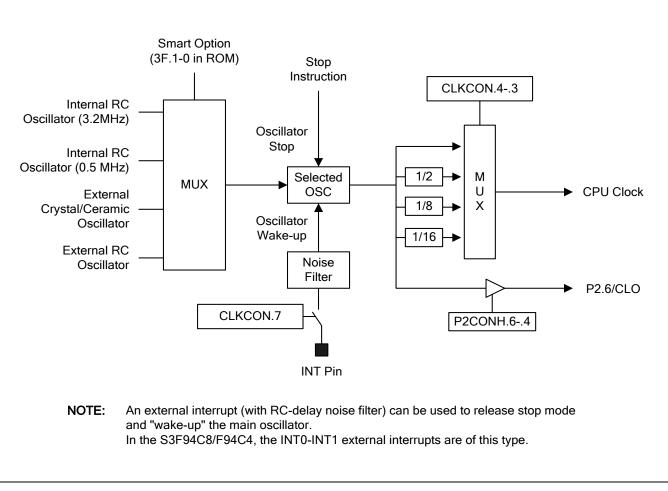

|       | ck Circuit                                                                |      |

| 7.1   | Overview                                                                  | 7-1  |

| 7.2   | Main Oscillator Logic                                                     | 7-1  |

|       | 7.2.1 Clock Status During Power-Down Modes                                |      |

|       | 7.2.2 System Clock Control Register                                       | 7-2  |

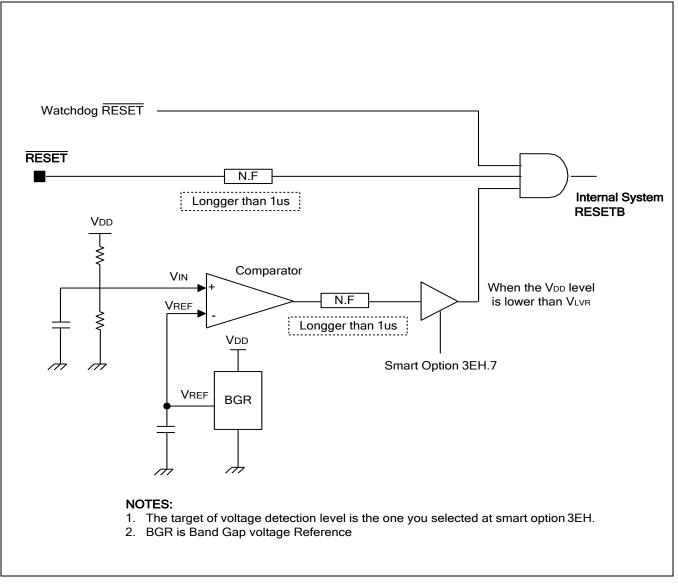

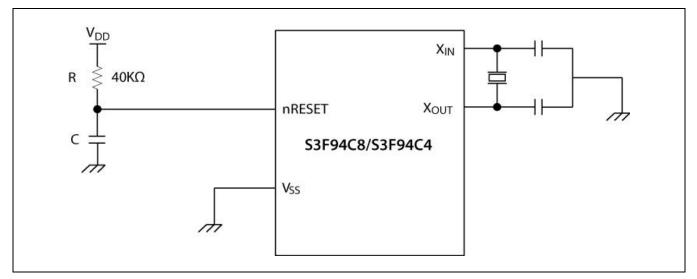

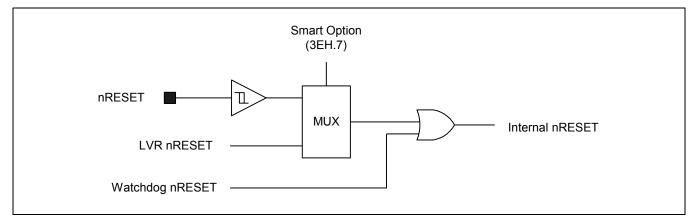

| 8 RES | SET and Power-Down                                                        |      |

|       | System Reset                                                              |      |

|       | 8.1.1 External RESET pin                                                  |      |

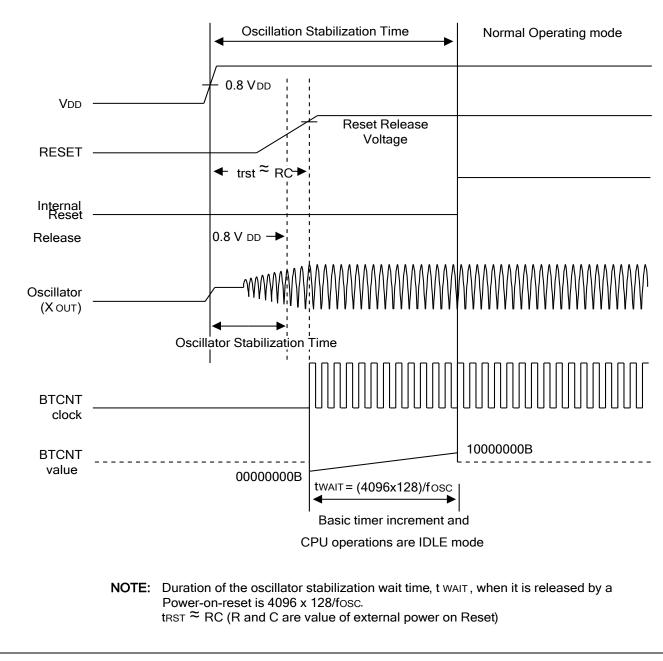

|       | 8.1.2 MCU Initialization Sequence                                         |      |

| 82    | Power-Down Modes                                                          |      |

| 0.2   | 8.2.1 Stop Mode                                                           |      |

|       | 8.2.2 Using RESET to Release Stop Mode                                    |      |

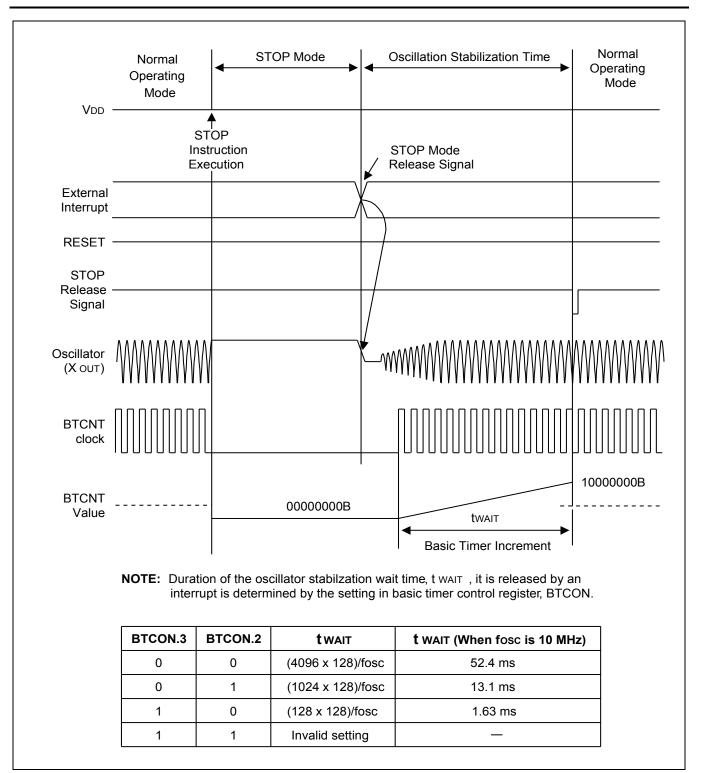

|       | 8.2.3 Using an External Interrupt to Release Stop Mode                    |      |

|       | 8.2.4 Idle Mode                                                           |      |

| 8.3   | Hardware Reset Values                                                     |      |

| 9 I/O | Ports                                                                     | 9-1  |

|       | Overview                                                                  |      |

|       | Port Data Registers                                                       |      |

| 9.2   |                                                                           |      |

|       | 9.2.1 Port 0<br>9.2.2 Port 2                                              |      |

|       |                                                                           |      |

|       | asic Timer and Timer 0                                                    |      |

| 10.1  | 1 Module Overview                                                         | 10-1 |

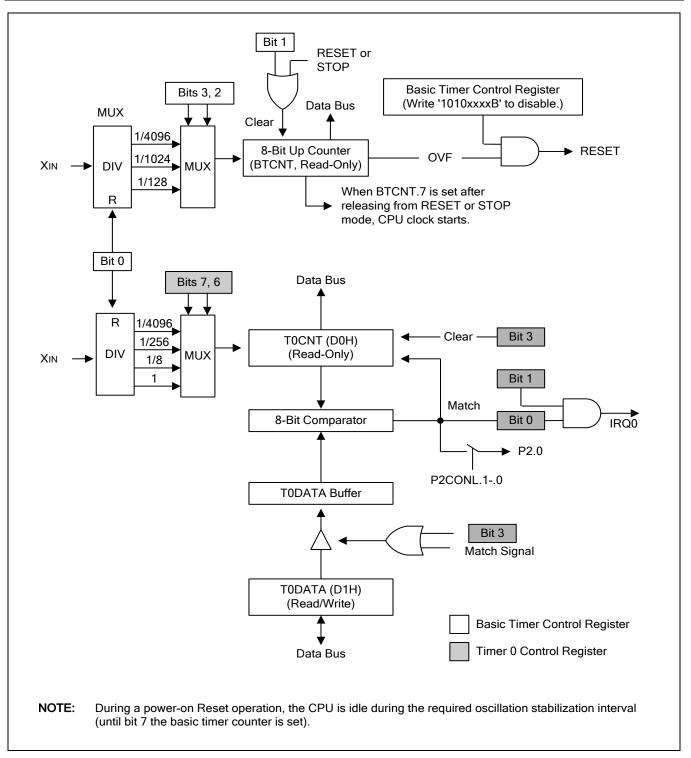

|       | 10.1.1 Basic Timer (BT)                                                   |      |

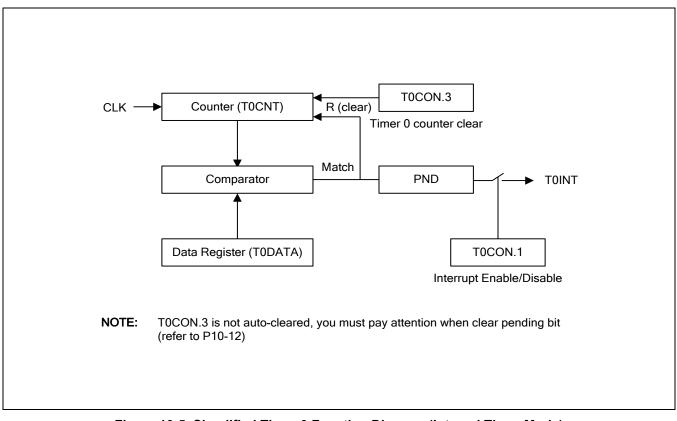

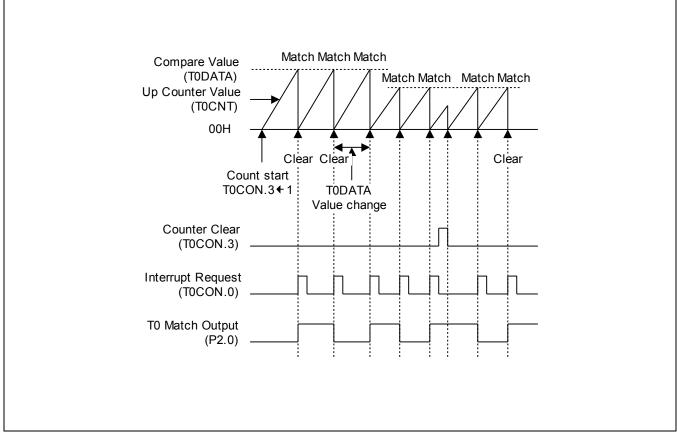

|       | 10.1.2 Timer 0                                                            | 10-1 |

| 10.2  | 2 Basic Timer                                                             | 10-2 |

|       | 10.2.1 Basic Timer Control Register                                       |      |

| 10.3  | 3 Basic Timer Function Description                                        |      |

|       | 10.3.1 Watchdog Timer Function                                            |      |

|       | 10.3.2 Oscillation Stabilization Interval Timer Function                  |      |

| 10.4 Timer 0                                                                              | 10-7  |

|-------------------------------------------------------------------------------------------|-------|

| 10.4.1 Timer 0 Control Registers                                                          | 10-7  |

| 10.5 Timer 0 Function Description                                                         | 10-8  |

| 10.5.1 Interval Timer Mode                                                                | 10-8  |

| 11 Pulse Width Modulation                                                                 | 11-1  |

| 11.1 Overview                                                                             | 11-1  |

| 11.2 Function Description                                                                 |       |

| 11.2.1 PWM                                                                                |       |

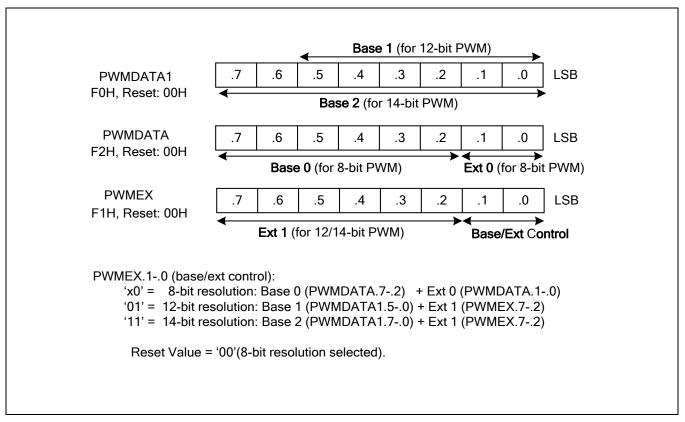

| 11.2.2 PWM Counter<br>11.2.3 PWM Data and Extension Registers                             |       |

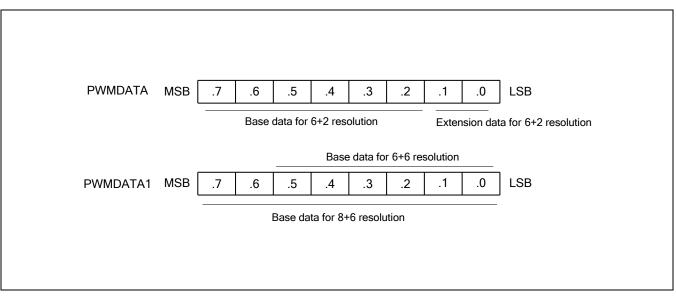

| Figure 11-1. PWM Data and Extension Registers                                             |       |

| 11.2.4 PWM Clock Rate                                                                     |       |

| 11.2.5 PWM Function Description                                                           | 11-3  |

| 11.2.6 PWM Output Waveform                                                                |       |

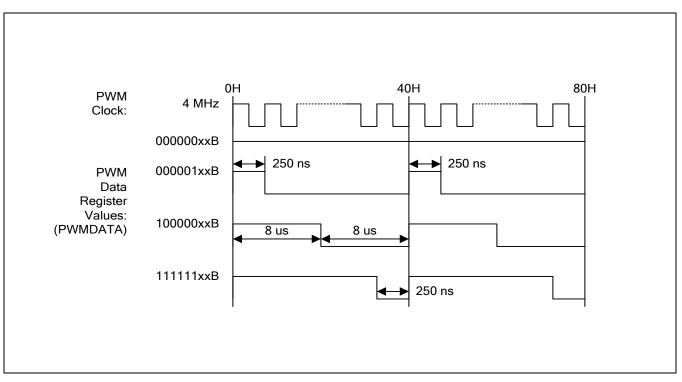

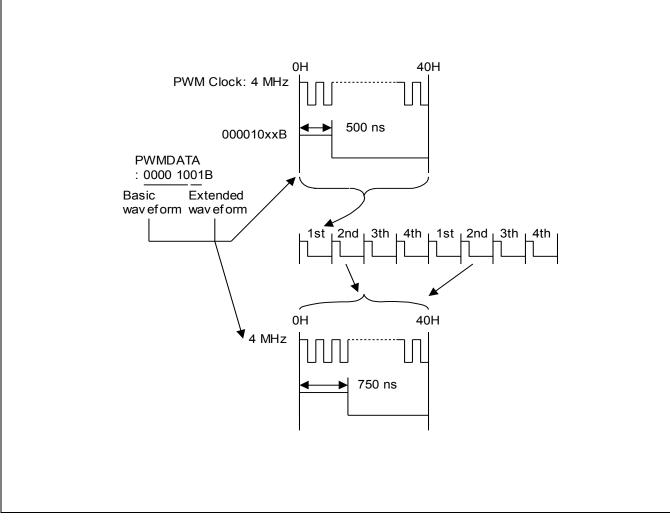

| Table 11-3. PWM output "stretch" Values for Extension Data bits Ext1 (PWMEX.72)           | 11-6  |

| Table 11-4. PWM output "stretch" Values for Extension Data bits Ext1 (PWMEX.72)           | 11-8  |

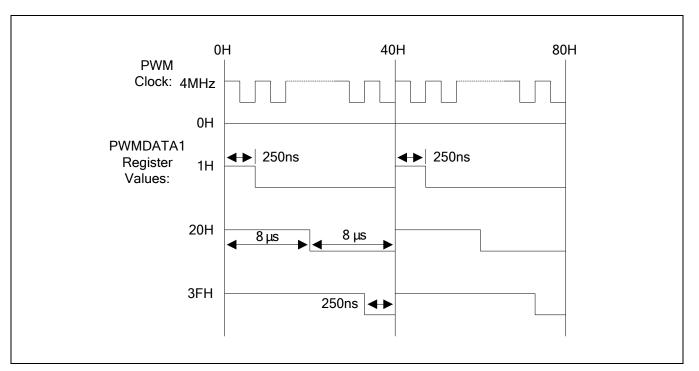

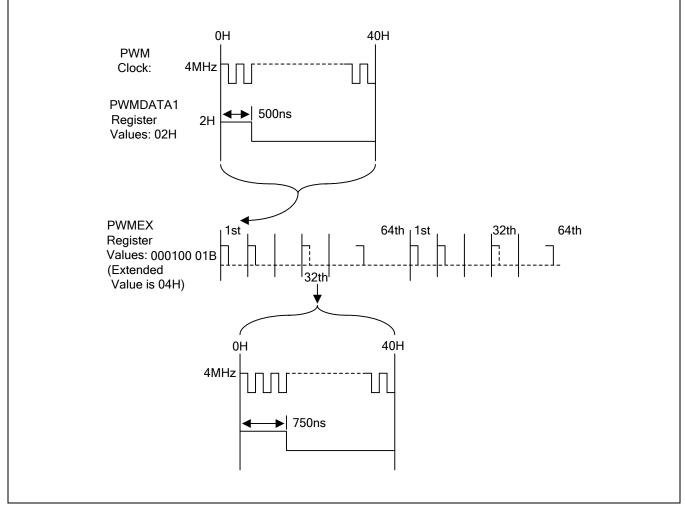

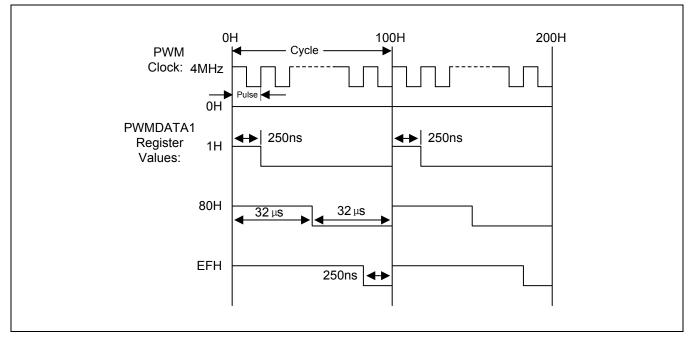

| Figure 11-6. PWM Basic Waveform (8-bit base)                                              | 11-8  |

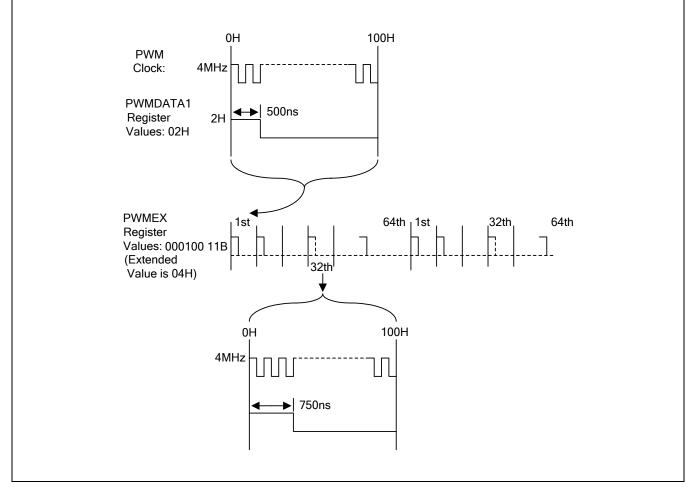

| Figure 11-7. PWM Basic Waveform (8-bit base + 6-bit extension)                            | 11-9  |

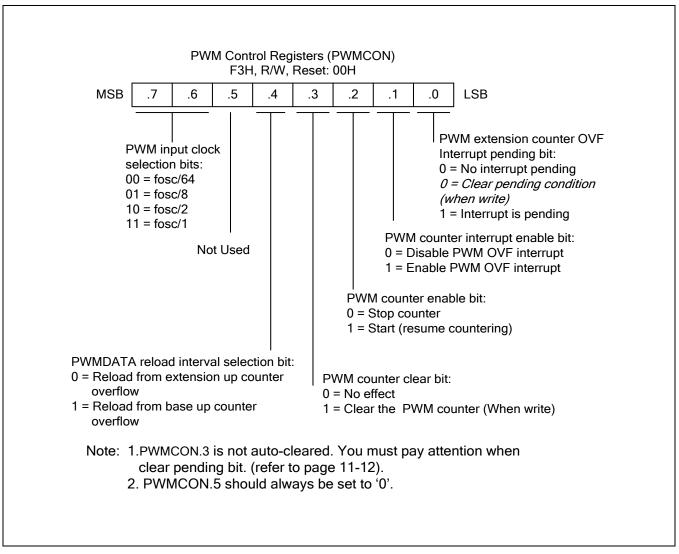

| 11.2.7 PWM Control Register                                                               | 11-10 |

| Figure 11-8. PWM Control Register (PWMCON)                                                |       |

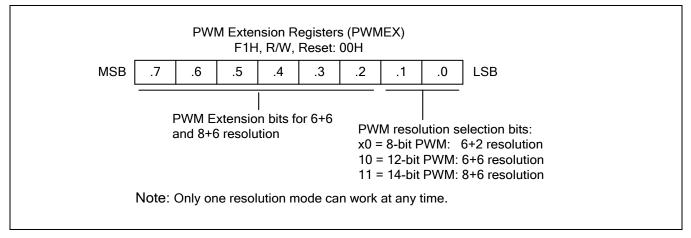

| 11.2.8 PWM Extension Register (PWMex)                                                     | 11-10 |

| Figure 11-9. PWM Extension Register (PWMEX)                                               | 11-11 |

| Figure 11-10. PWM Data Register (PWMDATA)                                                 | 11-11 |

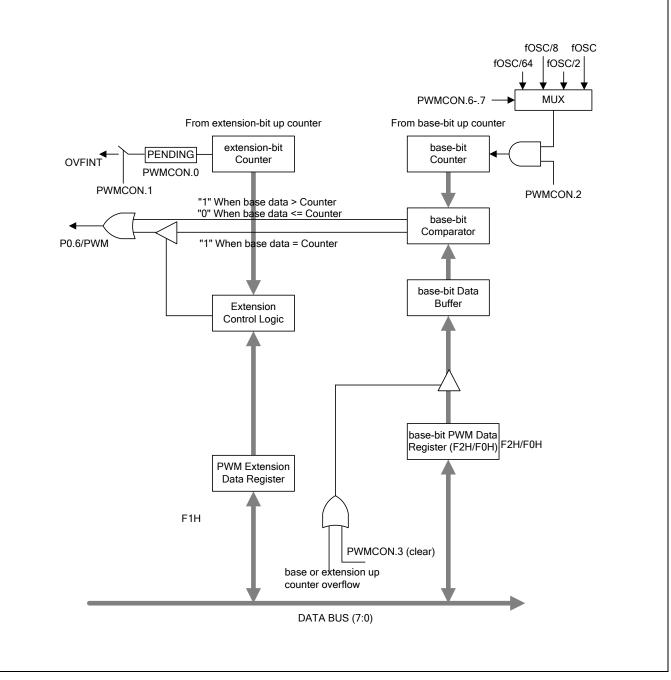

| Figure 11-12. PWM Module Functional Block Diagram                                         | 11-12 |

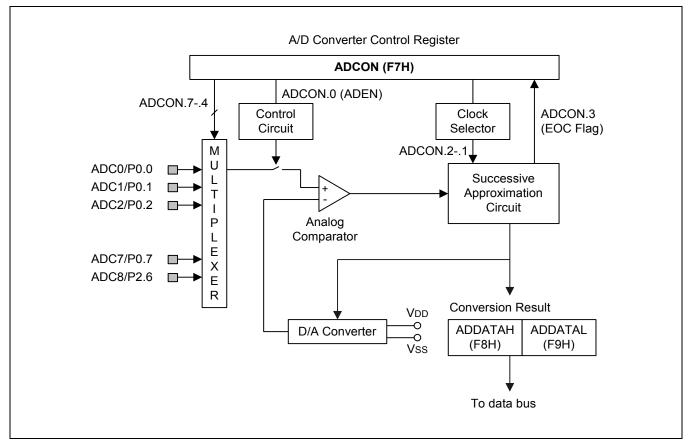

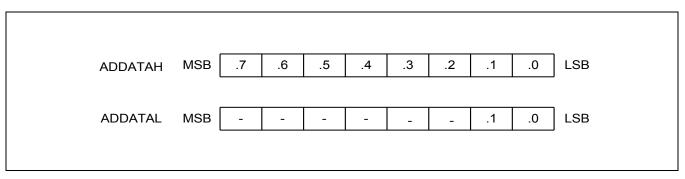

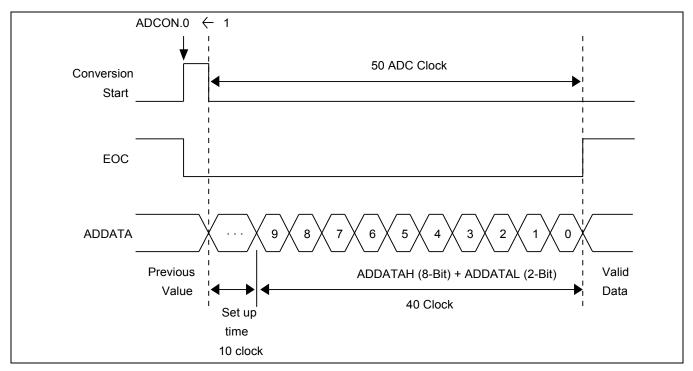

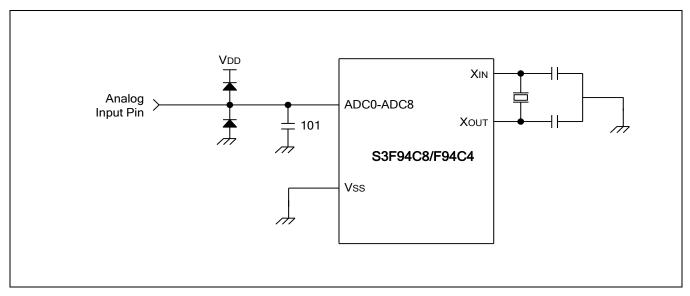

| 12 A/D Converter                                                                          | 12-1  |

| 12.1 Overview                                                                             | 12-1  |

| 12.1.1 Using A/D Pins for Standard digital Input                                          |       |

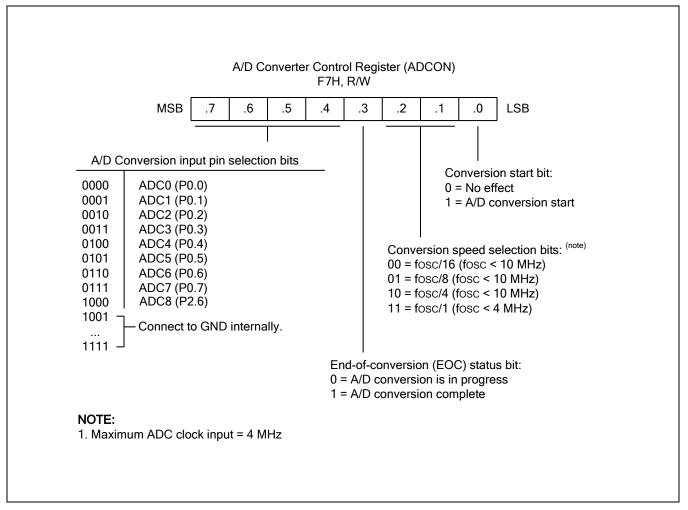

| 12.1.2 A/D Converter Control Register (ADCON)<br>12.1.3 Internal Reference Voltage Levels |       |

| 12.1.4 Conversion timing                                                                  |       |

| 12.1.5 Internal A/D Conversion Procedure                                                  | 12-5  |

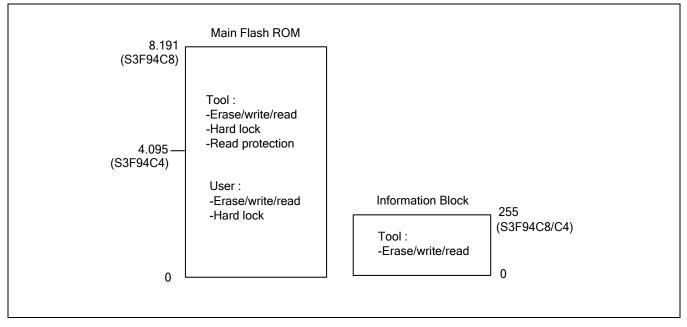

| 13 Embedded Flash Memory Interface                                                        | 13-1  |

| 13.1 Overview                                                                             |       |

| 13.1.1 Flash ROM Configuration                                                            |       |

| 13.1.2 Tool Program Mode<br>13.1.3 User Program Mode                                      |       |

| 13.2 Flash Memory Control Registers, User Program Mode                                    |       |

| 13.2.1 Flash Memory Control Register                                                      | 13-2  |

| 13.2.2 Flash Memory User Programming Enable Register                                      |       |

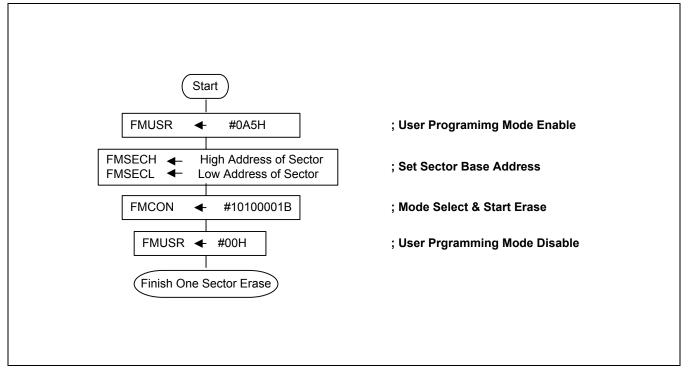

| 13.2.3 Flash Memory Sector Address Registers<br>13.3 Sector Erase                         |       |

| 13.3 Sector Erase                                                                         |       |

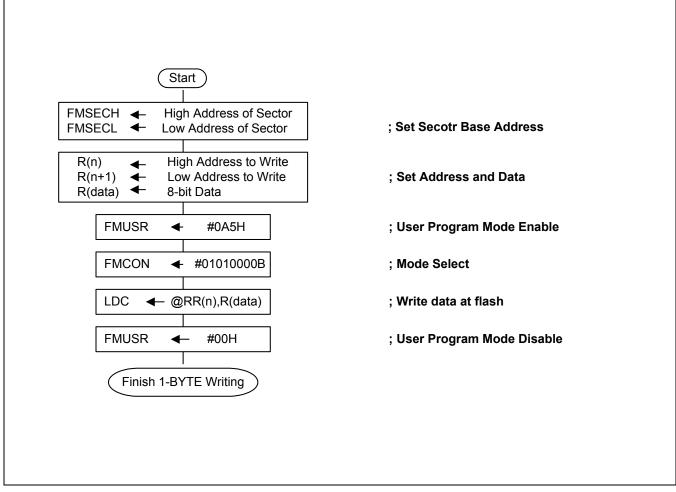

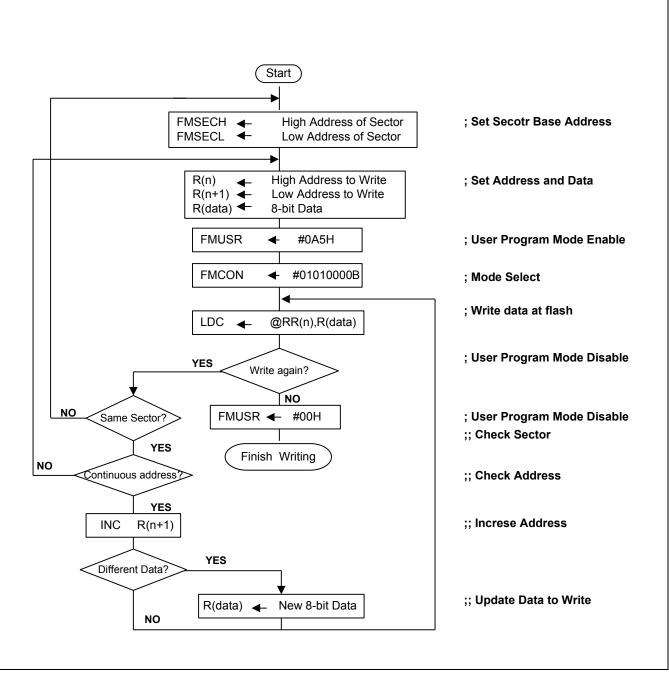

| 13.4.1 Program Procedure In User Program Mode                                             |       |

| 13.5 Reading                                                                              |       |

| 13.5.1 Program Procedure In User Program Mode                                             |       |

| 13.6 Hard Lock Protection                                    | 13-13 |

|--------------------------------------------------------------|-------|

| 13.6.1 Program Procedure In User Program Mode                | 13-13 |

| 14 Electrical Data                                           |       |

| 14.1 Overview                                                | 14-1  |

| 14.2 Table 14-11. Flash Memory AC Electrical Characteristics | 14-11 |

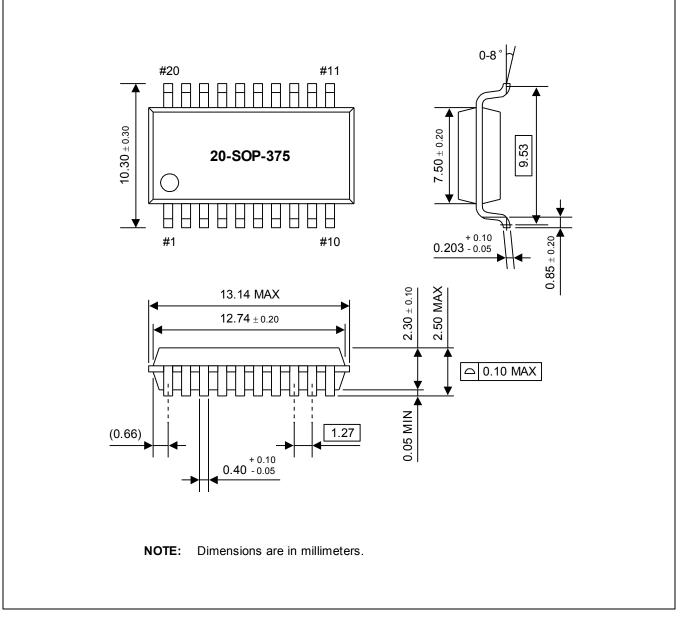

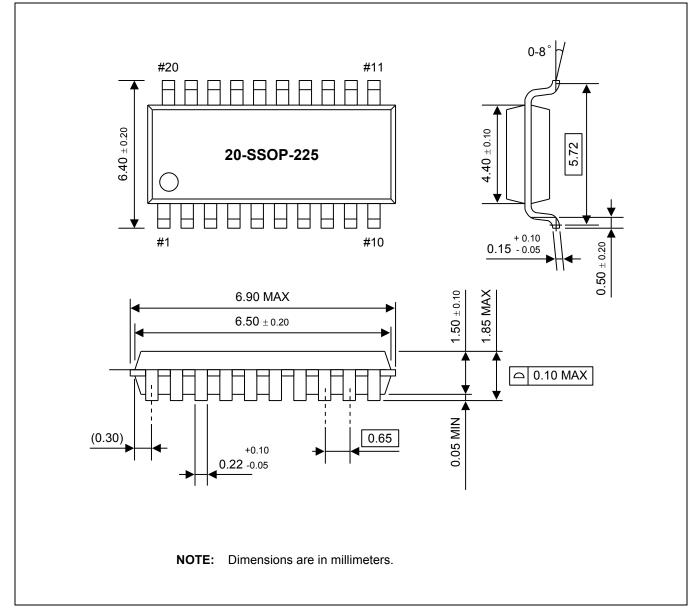

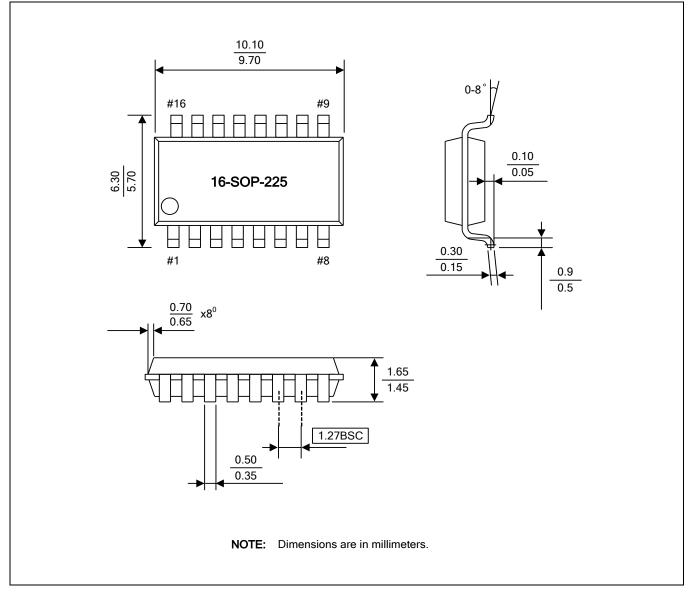

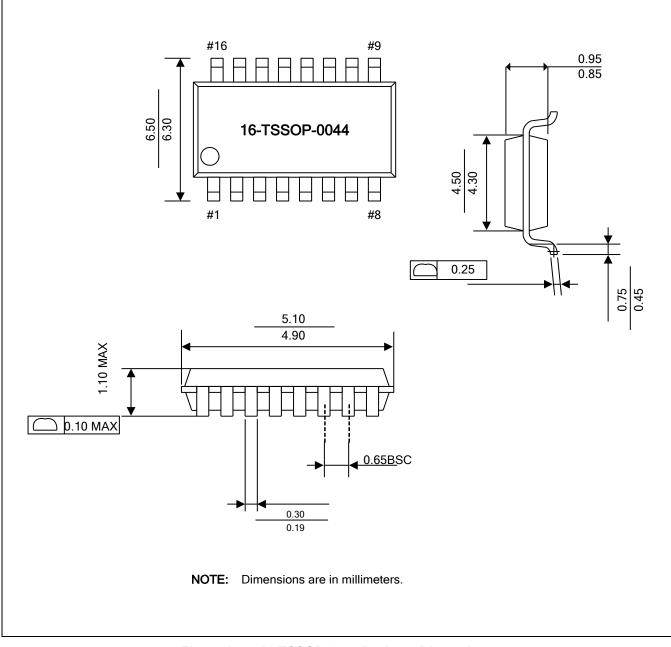

| 15 Mechanical Data                                           | 15-1  |

| 16 S3F94C8/S3F94C4 Flash MCUs                                | 16-1  |

| 16.1 Overview                                                | 16-1  |

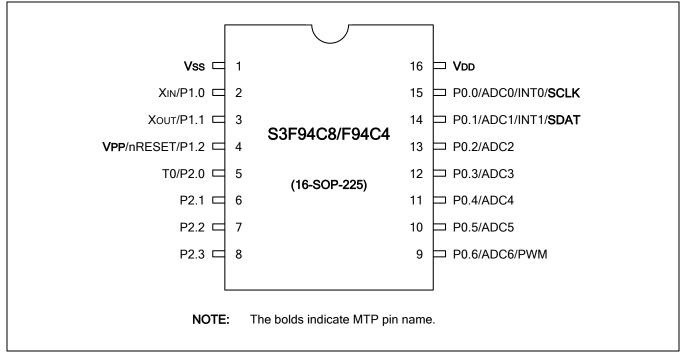

| 16.2 On-Board Writing                                        | 16-4  |

| 16.2.1 Circuit Design Guide                                  | 16-4  |

| 16.3 Information Block                                       | 16-5  |

| 17 Development Tools                                         | 17-1  |

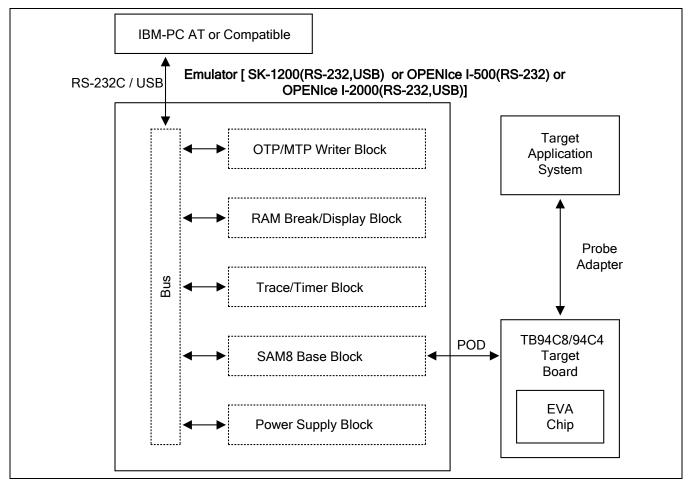

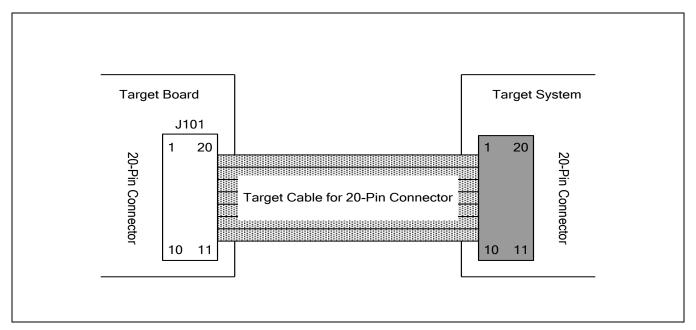

| 17.1 Target Boards                                           | 17-1  |

| 17.2 Programming Socket Adapter                              | 17-1  |

| 17.2.1 Development System Configuration                      | 17-2  |

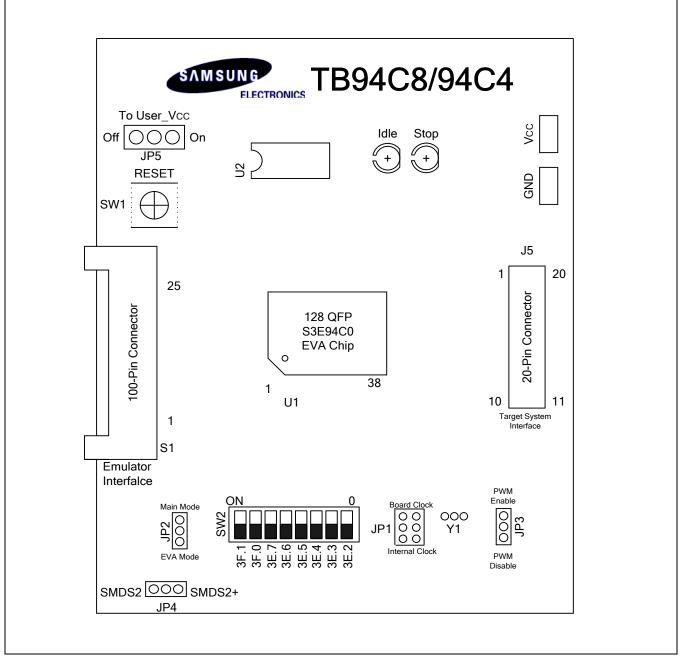

| 17.2.2 TB94C8/94C4 Target Board                              |       |

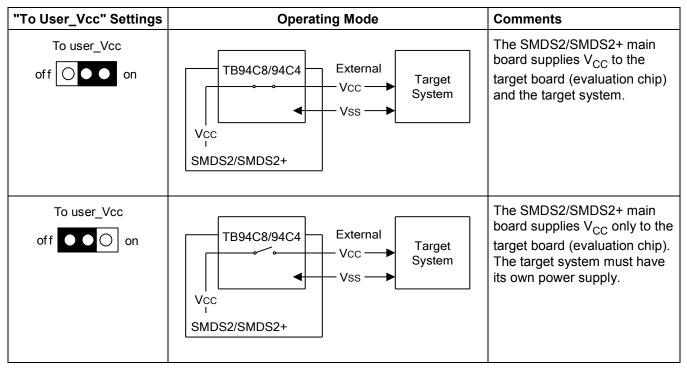

| 17.2.3 SMDS2+ Selection (SAM8)                               |       |

| 17.2.4 Third Parties for Development Tools                   |       |

| 17.2.5 In-Circuit Emulators                                  |       |

| 17.2.6 OTP/MTP Programmers                                   | 17-9  |

# **List of Figures**

| Figure<br>Number | Title                                                             | Page<br>Number |

|------------------|-------------------------------------------------------------------|----------------|

| Figure 1-        | . Block Diagram                                                   | 1-3            |

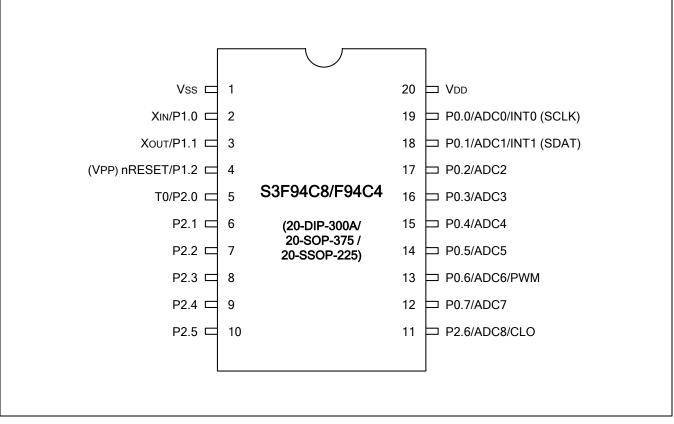

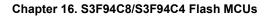

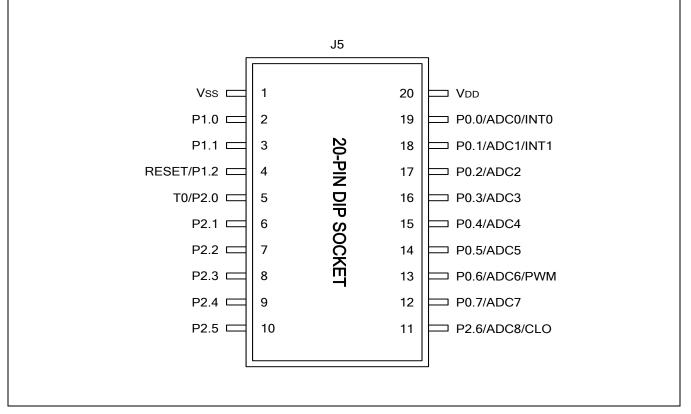

| Figure 1-2       | 2. Pin Assignment Diagram, 20-Pin DIP/SOP/SSOP Packages           |                |

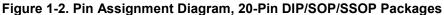

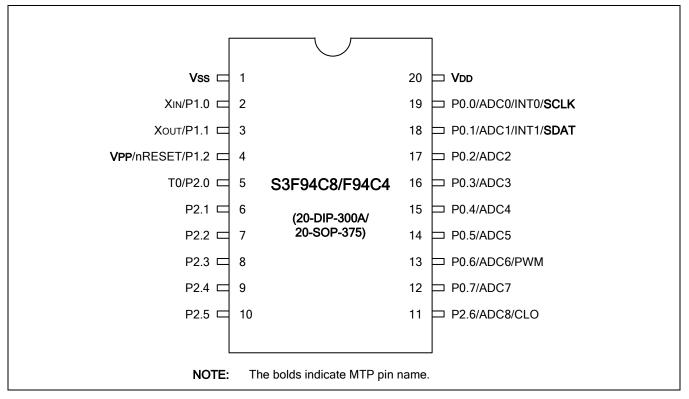

| Figure 1-3       | B. Pin Assignment Diagram, 16-Pin SOP/TSSOP Packages              | 1-5            |

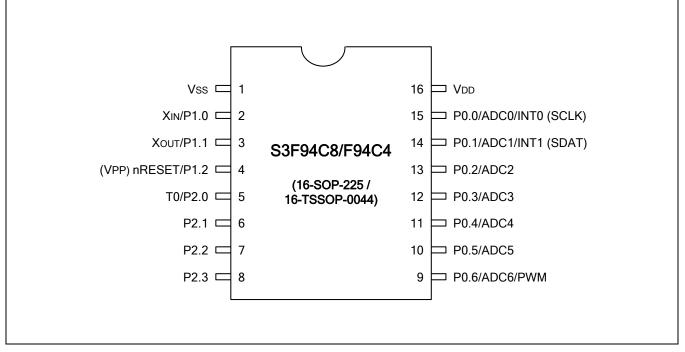

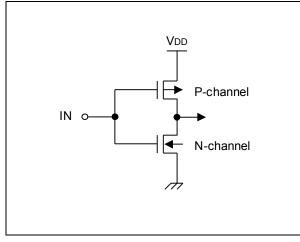

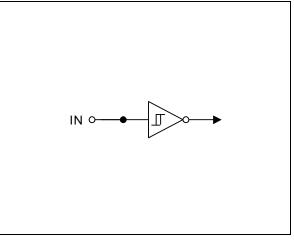

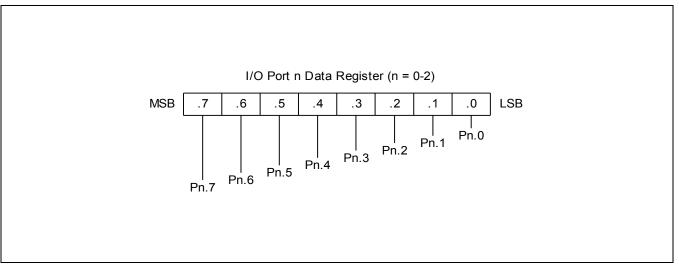

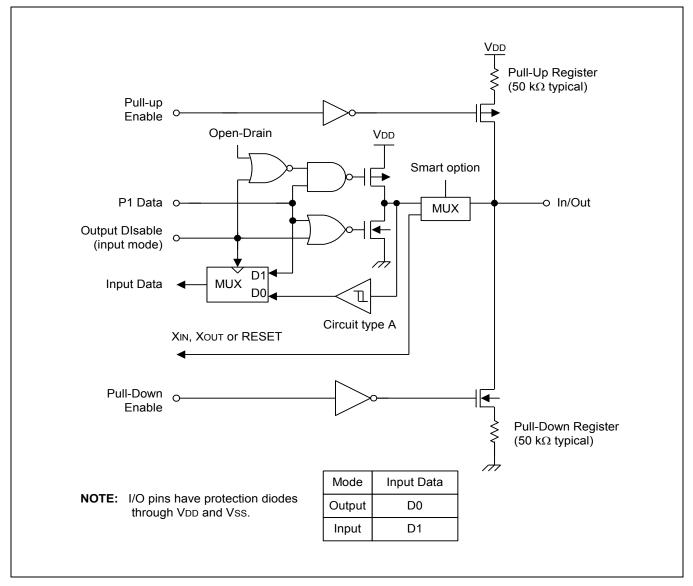

|                  | I. Pin Circuit Type A                                             |                |

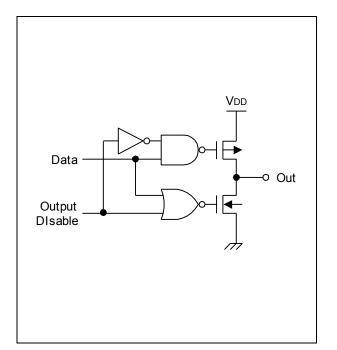

|                  | 5. Pin Circuit Type B (P1.2)                                      |                |

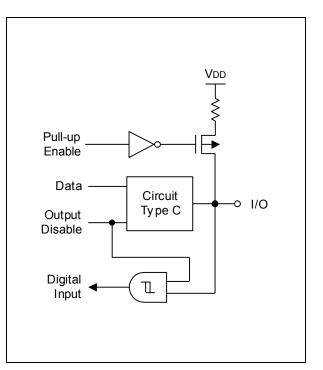

|                  | 6. Pin Circuit Type C                                             |                |

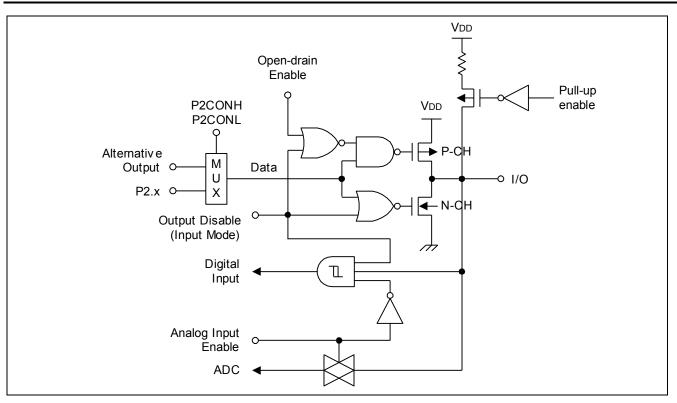

|                  | 7. Pin Circuit Type D                                             |                |

|                  | 3. Pin Circuit Type E (Port 2)                                    |                |

| Figure 1-9       | 9. Pin Circuit Type E-1 (Port 0)                                  |                |

| Figure 1-7       | 10. Pin Circuit Type E-2 (P1.0-P1.1)                              | 1-9            |

|                  | Program Memory Address Space                                      |                |

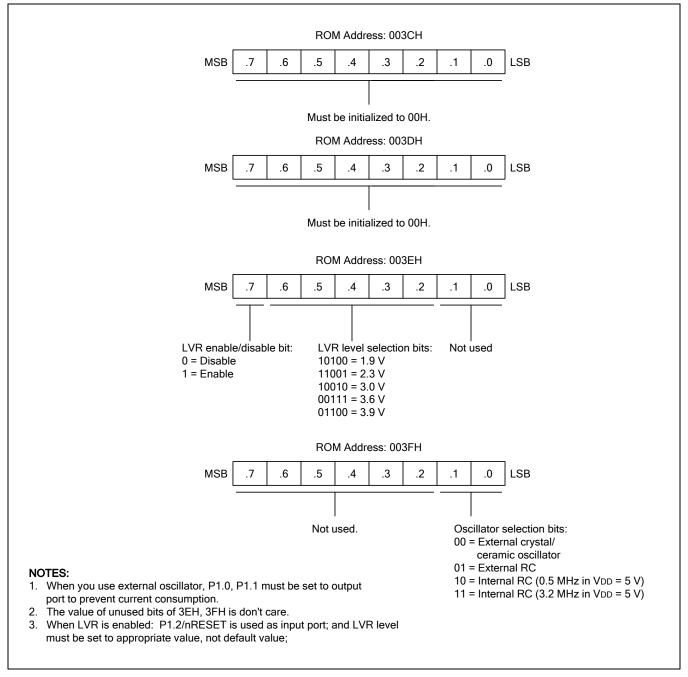

|                  | 2. Smart Option                                                   |                |

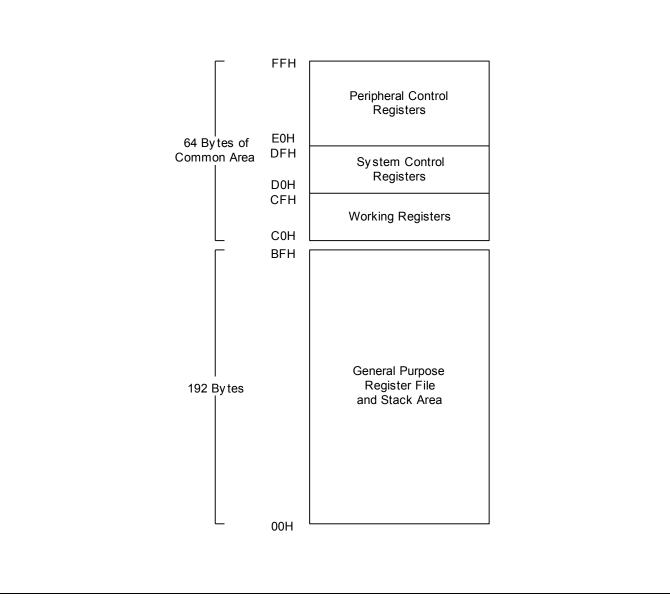

|                  | 3. Internal Register File Organization                            |                |

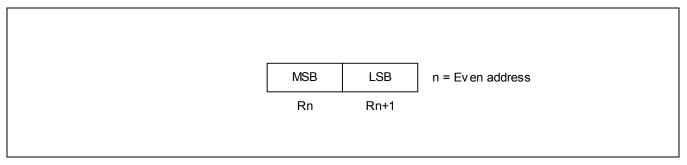

|                  | I. 16-Bit Register Pairs                                          |                |

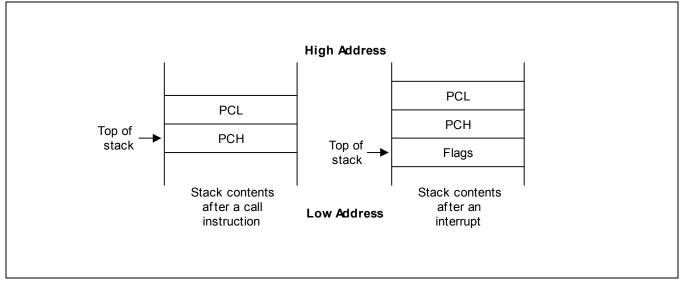

| Figure 2-8       | 5. Stack Operations                                               | 2-8            |

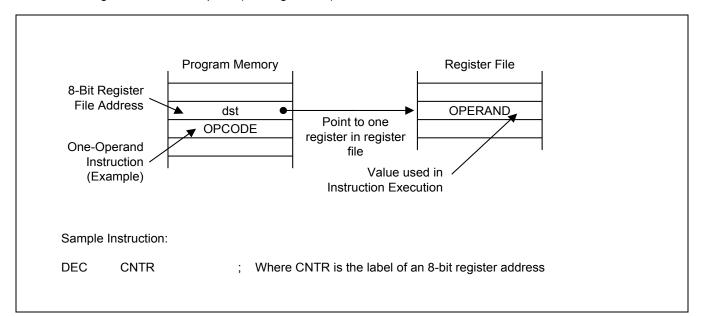

|                  | I. Register Addressing                                            |                |

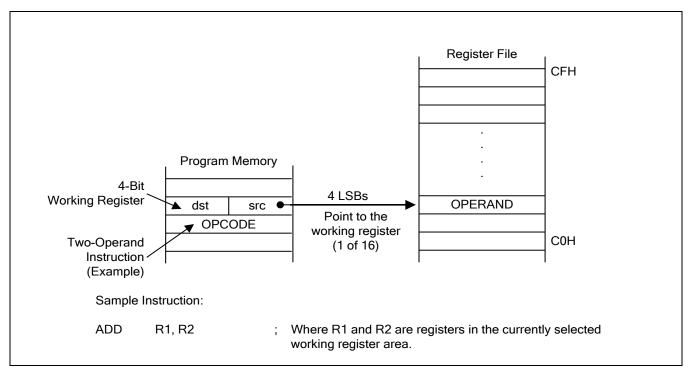

|                  | 2. Working Register Addressing                                    |                |

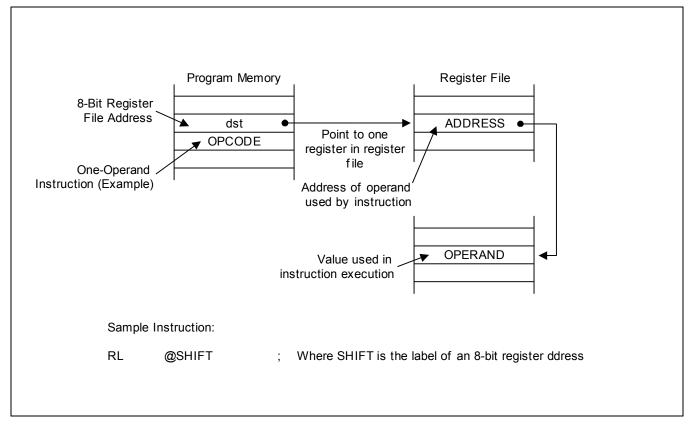

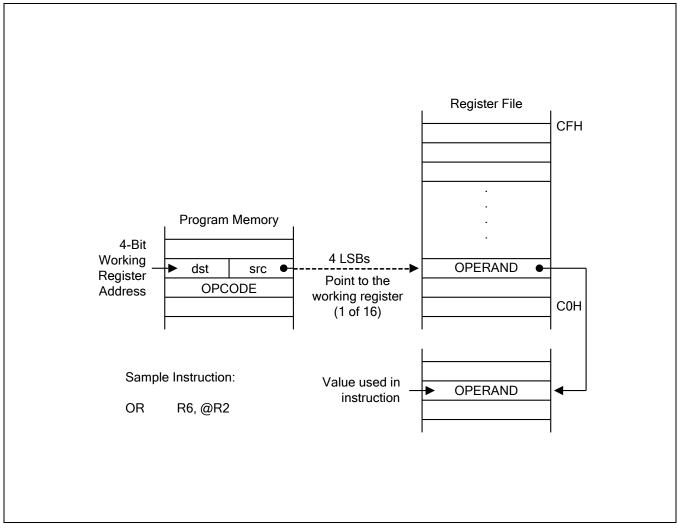

|                  | Indirect Register Addressing to Register File                     |                |

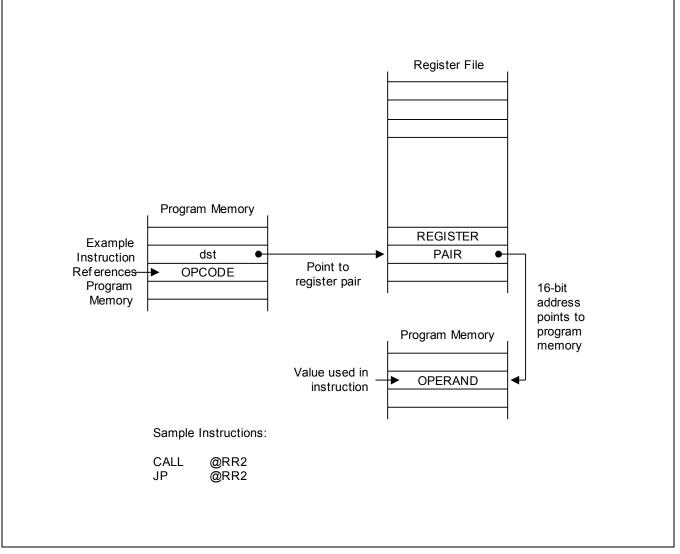

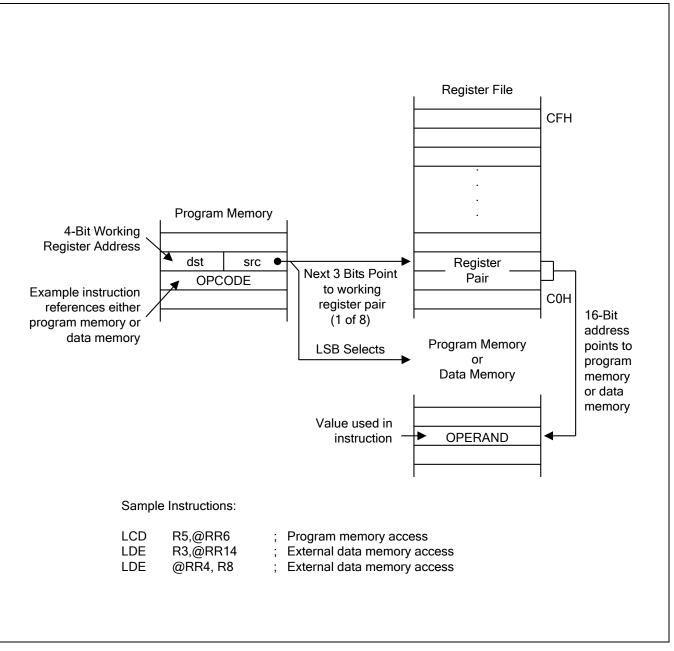

|                  | I. Indirect Register Addressing to Program Memory                 |                |

|                  | 5. Indirect Working Register Addressing to Register File          |                |

|                  | 6. Indirect Working Register Addressing to Program or Data Memory |                |

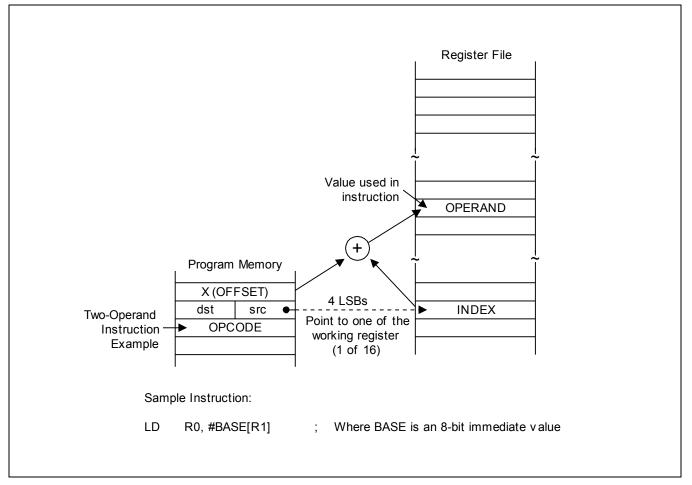

|                  | 7. Indexed Addressing to Register File                            |                |

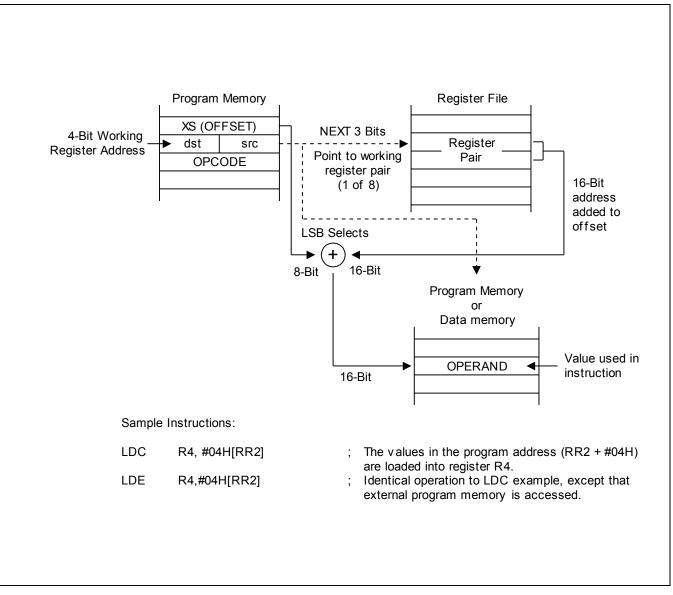

|                  | 8. Indexed Addressing to Program or Data Memory with Short Offset |                |

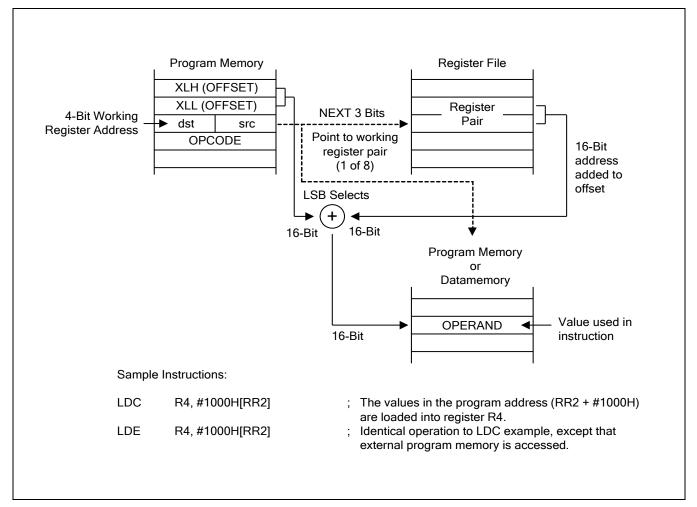

|                  | D. Indexed Addressing to Program or Data Memory with Long Offset  |                |

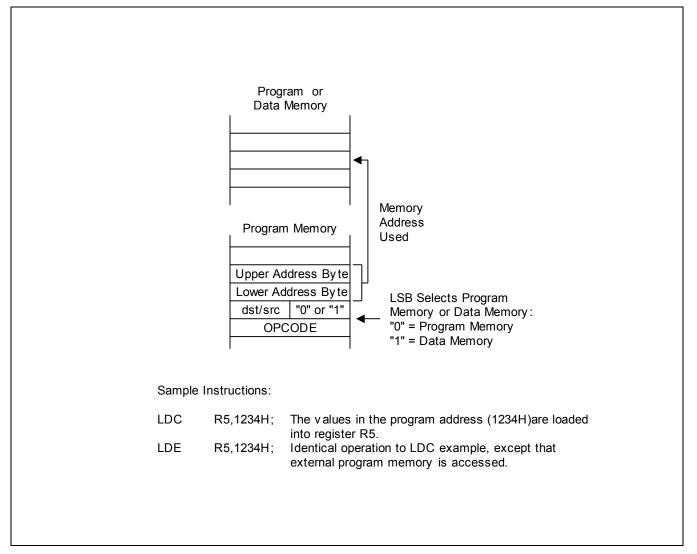

|                  | 0. Direct Addressing for Load Instructions.                       |                |

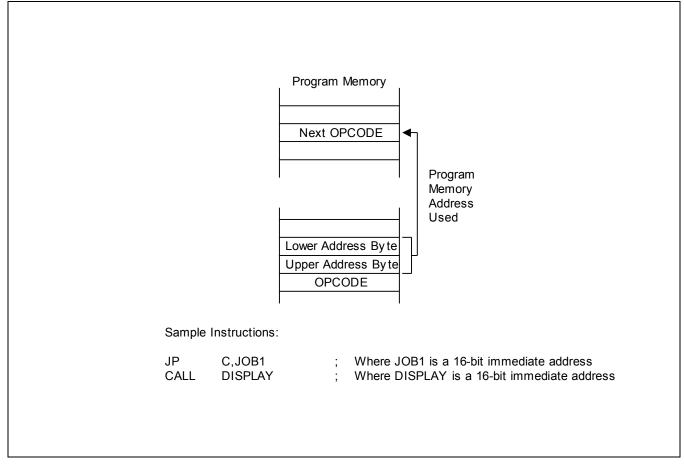

|                  | 1. Direct Addressing for Call and Jump Instructions               |                |

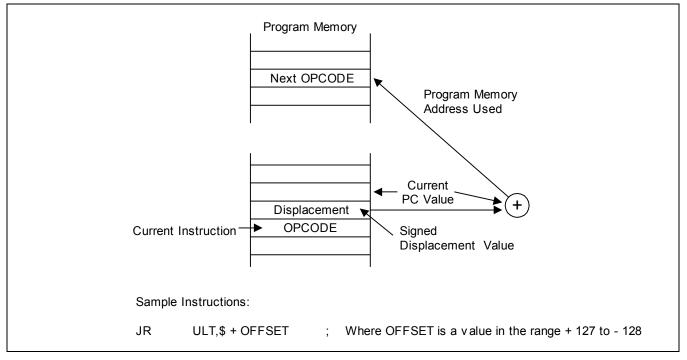

|                  | 2. Relative Addressing                                            |                |

| Figure 5-        | 3. Immediate Addressing                                           |                |

| Figure 4-7       | I. Register Description Format                                    | 4-4            |

| Figure 5-2       | . S3F9-Series Interrupt Type                                      | 5-1            |

|                  | 2. Interrupt Function Diagram                                     |                |

| Figure 5-3       | 3. S3F94C8/S3F94C4 Interrupt Structure                            | 5-4            |

| Figure 6-2       | I. System Flags Register (FLAGS)                                  | 6-4            |

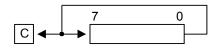

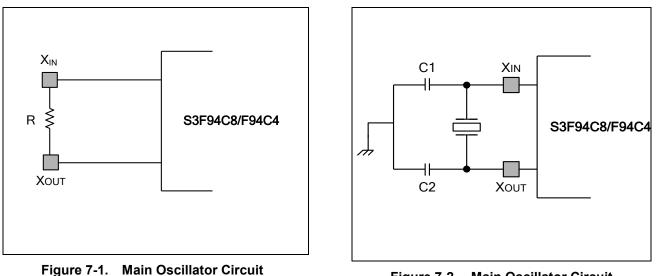

| Figure 7-2       | . Main Oscillator Circuit (RC Oscillator with Internal Capacitor) | 7-1            |

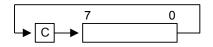

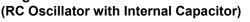

|                  | 2. Main Oscillator Circuit (Crystal/Ceramic Oscillator)           |                |

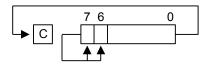

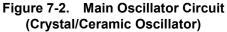

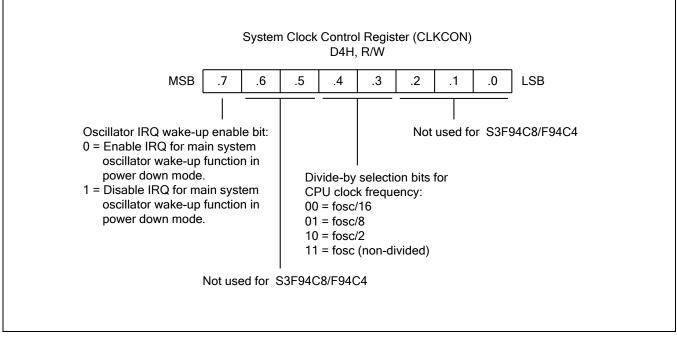

|                  | B. System Clock Control Register (CLKCON)                         |                |

|                  | I. System Clock Circuit Diagram                                   |                |

| Figure 8-2       | 2. Recommended External RESET Circuit                             |                |

|                  | 3. Reset Block Diagram                                            |                |

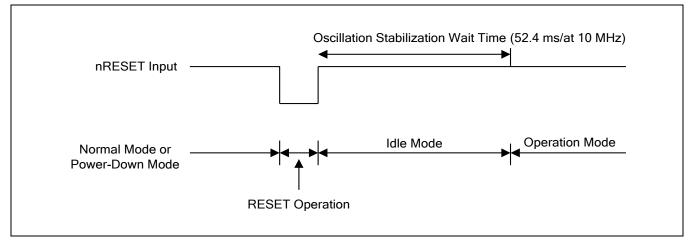

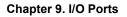

| Figure 9-1. Port Data Register Format.         9-2           Figure 9-2. Port 0 Control Register (POCONH, High Byte).         9-3           Figure 9-3. Port 0 Control Register (POCONL, Low Byte).         9-5           Figure 9-4. Port 0 Control Register (POCONL, Low Byte).         9-5           Figure 9-5. Port 1 Control Register (POCON).         9-6           Figure 9-6. Port 1 Control Register (POCON).         9-7           Figure 9-1. Port 1 Control Register (POCON).         9-8           Figure 9-1. Port 2 Control Register (PCCON).         9-9           Figure 9-1. Port 2 Control Register (PCCON).         9-10           Figure 9-1. Port 2 Control Register (PCCON).         10-2           Figure 0-2. Socillation Stabilization Time on RESET         10-4           Figure 10-3. Socillation Stabilization Time on RESET         10-4           Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)         10-7           Figure 10-7. Basic Timer and Timer 0 Bioke Diagram         10-10           Figure 11-1. PVM Data and Extension Registers         11-2           Figure 11-1. PVM Basic Waveform (6-bit base)         11-4           Figure 11-3. Extended PVMW Waveform (6-bit base + 2-bit extension)         11-7           Figure 11-4. PVM Basic Waveform (6-bit base + 2-bit extension)         11-7           Figure 11-1. PVM Masic Waveform (6-bit base + 2-bit extensio     | Figure 8-4. Timing for S3F94C8/S3F94C4 After RESET                           |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|

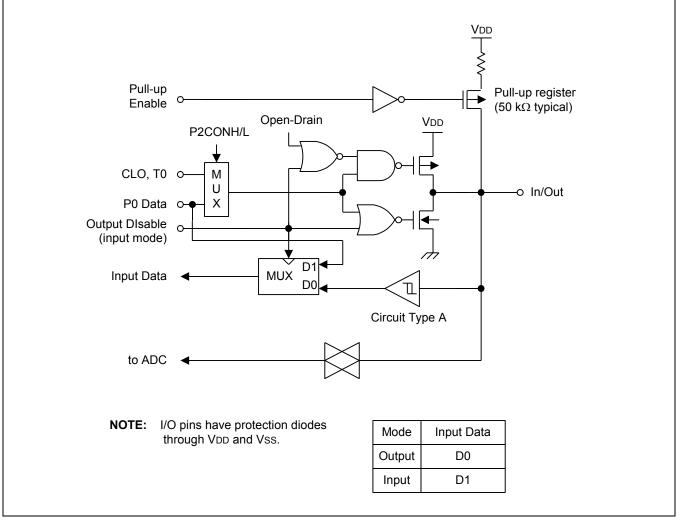

| Figure 9-2. Port 0 Circuit Diagram.       9-3         Figure 9-3. Port 0 Control Register (PCCONH, High Byte).       9-4         Figure 9-4. Port 0 Control Register (PCCONH, Low Byte).       9-5         Figure 9-5. Port 1 Circuit Diagram.       9-6         Figure 9-7. Port 1 Circuit Diagram.       9-7         Figure 9-7. Port 1 Circuit Diagram.       9-8         Figure 9-8. Port 2 Circuit Diagram.       9-9         Figure 9-1. Dort 2 Control Register (PCCONL, Low Byte).       9-11         Figure 10-1. Basic Timer Control Register (BTCON).       10-2         Figure 10-2. Oscillation Stabilization Time on Stop Mode Release       10-5         Figure 10-3. Simplified Timer 0 Function Diagram (Interval Timer Mode).       10-7         Figure 10-4. Timer 0 Timing Diagram.       10-10         Figure 11-2. PWM Basic Waveform (6-bit base).       11-4         Figure 11-1. PWM Data and Extension Registers.       11-2         Figure 11-2. PWM Basic Waveform (6-bit base).       11-6         Figure 11-2. PWM Basic Waveform (6-bit base).       11-6         Figure 11-1. PWM Basic Waveform (6-bit base).       11-6         Figure 11-2. PWM Basic Waveform                                                                                   | Figure 9-1. Port Data Register Format                                        |       |

| Figure 9-3. Port 0 Control Register (POCONL, Low Byte)       9-4         Figure 9-4. Port 0 Control Register (POCONL, Low Byte)       9-5         Figure 9-5. Port 0 Interrupt Pending Registers (POPND)       9-6         Figure 9-5. Port 1 Control Register (PICON)       9-8         Figure 9-7. Port 1 Control Register (PICON)       9-8         Figure 9-8. Port 2 Control Register (PICON)       9-8         Figure 9-7. Port 1 Control Register (PICON)       9-10         Figure 9-8. Port 2 Control Register (PICON)       9-10         Figure 9-10. Port 2 Control Register (PICON)       9-10         Figure 10-1. Basic Timer Control Register (BTCON)       10-2         Figure 10-3. Oscillation Stabilization Time on RESET       10-4         Figure 10-4. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-7         Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-9         Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-3. Extended PWM Waveform (6-bit base + 2-bit extension)       11-1         Figure 11-4. PWM Basic Waveform (6-bit base + 6-bit extension)       11-1         Figure 11-5. Extended PWM Waveform (6-bit base + 6-bit extension)       11-1         Figure 11-1. PWM Data and Extension Register (PWMDAD)       11-11         Figure 11-2. PWM Basic Waveform (6-bit base + 6-bit extension)                             |                                                                              |       |

| Figure 9-4. Port 0         Control Register (POCONL, Low Byte)         9-5           Figure 9-5. Port 1         Circuit Diagram         9-7           Figure 9-6. Port 1         Circuit Diagram         9-7           Figure 9-8. Port 2         Circuit Diagram         9-8           Figure 9-8. Port 2         Circuit Diagram         9-9           Figure 9-9. Port 2         Control Register (PCONL, Low Byte)         9-10           Figure 9-10. Port 2         Control Register (BTCON)         10-2           Figure 10-1. Basic Timer Control Register (BTCON)         10-2         Figure 10-3. Oscillation Stabilization Time on RESET         10-4           Figure 10-2. Oscillation Stabilization Time on Stop Mode Release         10-5         Figure 10-6. Timer 0 Control Register (TOCON)         10-2           Figure 10-7. Basic Timer and Timer 0 Elock Diagram         10-4         Figure 10-7. Basic Timer and Timer 0 Block Diagram         10-10           Figure 11-1. PVMD Bata and Extension Register (BMCON)         11-2         Figure 11-3. Extended PWM Waveform (6-bit base)         11-4           Figure 11-3. Extended PWM Waveform (6-bit base)         11-6         Figure 11-1. PVM Bata waveform (6-bit base)         11-6           Figure 11-1. PVM Masic Waveform (6-bit base)         11-16         Figure 11-1. PVM Masic Waveform (6-bit base)         11-17           Figure 11-1. PVM Masic W |                                                                              |       |

| Figure 9-5. Port 0 Interrupt Pending Registers (POPND)         9-6           Figure 9-7. Port 1 Control Register (P1CON)         9-7           Figure 9-7. Port 1 Control Register (P1CON)         9-8           Figure 9-8. Port 2 Circuit Diagram         9-9           Figure 9-9. Port 2 Control Register (P2CONL, Low Byte)         9-10           Figure 9-10. Port 2 Control Register (P2CONL, Low Byte)         9-11           Figure 10-1. Basic Timer Control Register (BTCON)         10-2           Figure 10-3. Oscillation Stabilization Time on RSEST         10-4           Figure 10-3. Oscillation Stabilization Time on Stop Mode Release         10-5           Figure 10-4. Simplified Timer 0 Function Diagram (Interval Timer Mode)         10-7           Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)         10-8           Figure 11-1. PWM Data and Extension Registers         11-2           Figure 11-1. PWM Data and Extension Registers         11-2           Figure 11-2. PVM Basic Waveform (6-bit base)         11-6           Figure 11-4. PVM Mask Waveform (6-bit base)         11-6           Figure 11-5. PVM Basic Waveform (6-bit base)         11-7           Figure 11-6. PVM Basic Waveform (8-bit base)         11-7           Figure 11-7. PVM Data Register (PWMON)         11-16           Figure 11-1. PVM Mascont Register (PWMON)         11-17                       |                                                                              |       |

| Figure 9-6. Port 1 Circuit Diagram         9-7           Figure 9-7 Port 1 Control Register (P1CON)         9-8           Figure 9-8. Port 2 Circuit Diagram         9-9           Figure 9-9. Port 2 Control Register (P2CONL, Low Byte)         9-10           Figure 9-10. Port 2 Control Register (P2CONL, Low Byte)         9-11           Figure 9-10. Port 2 Control Register (P2CONL, Low Byte)         9-11           Figure 10-1. Basic Timer Control Register (BTCON)         10-2           Figure 10-2. Oscillation Stabilization Time on RtSET         10-4           Figure 10-3. Simplified Timer 0 Function Diagram (Interval Timer Mode)         10-7           Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)         10-8           Figure 10-7. Basic Timer and Timer 0 Block Diagram.         10-9           Figure 11-1. PVM Data and Extension Registers.         11-2           Figure 11-3. Extended PVM Waveform (6-bit base)         11-4           Figure 11-4. PVM Basic Waveform (6-bit base)         11-6           Figure 11-5. Extended PVM Waveform (6-bit base)         11-7           Figure 11-6. PVM Basic Waveform (6-bit base)         11-7           Figure 11-7. PVM Masic Waveform (6-bit base)         11-7           Figure 11-8. PVM Masic Waveform (6-bit base)         11-7           Figure 11-9. PVM Masic Waveform (6-bit base)         11-7                              | Figure 9-5. Port 0 Interrupt Pending Registers (P0PND)                       |       |

| Figure 9-7. Port 1 Control Register (P1CON).       9-8         Figure 9-8. Port 2 Circuil Diagram.       9-9         Figure 9-8. Port 2 Control Register (P2CONL, Low Byte).       9-10         Figure 9-10. Port 2 Control Register (P2CONL, Low Byte).       9-11         Figure 10-1. Basic Timer Control Register (BTCON).       10-2         Figure 10-3. Oscillation Stabilization Time on RSEST       10-4         Figure 10-4. Socialition Stabilization Time on Stop Mode Release       10-5         Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-7         Figure 10-6. Timer 0 Timing Diagram.       10-9         Figure 10-7. Basic Timer and Timer 0 Block Diagram.       10-10         Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-2. PVM Basic Waveform (6-bit base)       11-5         Figure 11-3. Extended PWM Waveform (6-bit base)       11-6         Figure 11-4. PVM Data and Extension Register (PWMCON)       11-16         Figure 11-5. Extended PWM Waveform (6-bit base)       11-6         Figure 11-8. PVM Extension Register (PWMCON)       11-17         Figure 11-8. PVM Extension Register (PWMCON)       11-17         Figure 11-1. PVM Data Register (PWMCON)       11-17         Figure 12-1. A/D Converter Control Register (ADCON)       12-2         Figure 12-2. A/D Converter Control Regis                                                |                                                                              |       |

| Figure 9-8. Port 2 Control Register (P2CONH, High Byte).       9-9         Figure 9-9. Port 2 Control Register (P2CONL, Low Byte).       9-10         Figure 10-1. Basic Timer Control Register (BTCON).       10-2         Figure 10-2. Oscillation Stabilization Time on RESET       10-4         Figure 10-3. Oscillation Stabilization Time on Stop Mode Release       10-5         Figure 10-4. Timer 0 Control Registers (TOCON).       10-7         Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-8         Figure 10-7. Basic Timer and Timer 0 Block Diagram.       10-9         Figure 11-1. PWM Data and Extension Registers.       11-2         Figure 11-2. PWM Basic Waveform (6-bit base)       11-4         Figure 11-3. Extended PWM Waveform (6-bit base)       11-6         Figure 11-4. PWM Basic Waveform (6-bit base)       11-6         Figure 11-5. Extended PWM Waveform (6-bit base)       11-6         Figure 11-6. PWM Basic Waveform (6-bit base)       11-7         Figure 11-7. PWM Data Register (PWMCX)       11-11         Figure 11-8. DWM Control Register (PWMCX)       11-11         Figure 11-9. PWM Extension Register (PWMCX)       11-11         Figure 12-1. A/D Converter Control Register (ADDCN)       12-2         Figure 12-3. A/D Converter Data Register (PWMCX)       11-11         Figure 13-4. Fissh Memory Sec                                                |                                                                              |       |

| Figure 9-10. Port 2 Control Register (P2CONL, Low Byte)       9-11         Figure 10-1. Basic Timer Control Register (BTCON)       10-2         Figure 10-2. Oscillation Stabilization Time on RESET       10-4         Figure 10-3. Oscillation Stabilization Time on Stop Mode Release       10-5         Figure 10-4. Timer 0 Control Registers (TCCON)       10-7         Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-8         Figure 10-6. Timer 0 Timing Diagram       10-9         Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-2. PWM Basic Waveform (6-bit base)       11-4         Figure 11-3. Extended PWM Waveform (6-bit base)       11-6         Figure 11-4. PWM Basic Waveform (6-bit base)       11-6         Figure 11-5. Extended PWM Waveform (6-bit base)       11-7         Figure 11-6. PWM Basic Waveform (6-bit base)       11-6         Figure 11-7       PWM Control Register (PWMCON)       11-1         Figure 11-8. PWM Control Register (PWMCON)       11-1         Figure 11-10. PWM Data Register (PWMEX)       11-11         Figure 11-2. PWM Module Functional Block Diagram       11-12         Figure 12-1. A/D Converter Control Register (ADCON)       12-2         Figure 12-2. A/D Converter Data Register (ADCON)       12-2         Figure 13-3. Flash Memory Sector Address R                                                         |                                                                              |       |

| Figure 10-1. Basic Timer Control Register (BTCON)       10-2         Figure 10-3. Oscillation Stabilization Time on RESET       10-4         Figure 10-3. Oscillation Stabilization Time on Stop Mode Release       10-5         Figure 10-4. Timer 0. Control Registers (TOCON)       10-7         Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-8         Figure 10-7. Basic Timer and Timer 0 Block Diagram       10-9         Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-1. Extended PWM Waveform (6-bit base)       11-4         Figure 11-5. Extended PWM Waveform (6-bit base)       11-6         Figure 11-6. PWM Basic Waveform (6-bit base)       11-6         Figure 11-7. PWM Basic Waveform (6-bit base)       11-8         Figure 11-8. Extended PWM Waveform (6-bit base)       11-6         Figure 11-8. PWM Basic Waveform (6-bit base)       11-7         Figure 11-8. PWM Basic Waveform (6-bit base)       11-7         Figure 11-8. PWM Basic Waveform (6-bit base)       11-1         Figure 11-9. PWM Basic Register (PWMCON)       11-1         Figure 11-15. Extended PWM Waveform (6-bit base)       11-1         Figure 11-2. PWM Data Register (PWMCON)       11-1         Figure 11-1. PWM Data Register (PWMCON)       11-11         Figure 11-2. PWM Module Functional Block Diagram       1                                                         |                                                                              |       |

| Figure 10-2 Oscillation Stabilization Time on RESET       10-4         Figure 10-3. Oscillation Stabilization Time on Stop Mode Release       10-5         Figure 10-4. Timer 0 Control Registers (T0CON)       10-7         Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-9         Figure 10-6. Timer 0 Timing Diagram       10-9         Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-2. PWM Basic Waveform (6-bit base)       114         Figure 11-3. Extended PWM Waveform (6-bit base)       11-6         Figure 11-4. PWM Basic Waveform (6-bit base)       11-6         Figure 11-5. Extended PWM Waveform (6-bit base)       11-6         Figure 11-6. PWM Basic Waveform (6-bit base)       11-1         Figure 11-6. PWM Basic Waveform (6-bit base)       11-1         Figure 11-7. PWM Basic Waveform (6-bit base)       11-1         Figure 11-8. PWM Control Register (PWMCN)       11-11         Figure 11-8. PWM Control Register (PWMEX)       11-11         Figure 11-10. PWM Data Register (PWMEX)       11-11         Figure 12-2. A/D Converter Control Register (ADCON)       12-2         Figure 12-3. A/D Converter Control Register (ADCON)       12-2         Figure 13-4. Flash Memory Sector Address Register (FMUSR)       13-2         Figure 13-4. Flash Memory Sector Address Register (FMUSR)                                                      | Figure 9-10. Port 2 Control Register (P2CONL, Low Byte)                      | 9-11  |

| Figure 10-2 Oscillation Stabilization Time on RESET       10-4         Figure 10-3. Oscillation Stabilization Time on Stop Mode Release       10-5         Figure 10-4. Timer 0 Control Registers (T0CON)       10-7         Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       10-9         Figure 10-6. Timer 0 Timing Diagram       10-9         Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-2. PWM Basic Waveform (6-bit base)       114         Figure 11-3. Extended PWM Waveform (6-bit base)       11-6         Figure 11-4. PWM Basic Waveform (6-bit base)       11-6         Figure 11-5. Extended PWM Waveform (6-bit base)       11-6         Figure 11-6. PWM Basic Waveform (6-bit base)       11-1         Figure 11-6. PWM Basic Waveform (6-bit base)       11-1         Figure 11-7. PWM Basic Waveform (6-bit base)       11-1         Figure 11-8. PWM Control Register (PWMCN)       11-11         Figure 11-8. PWM Control Register (PWMEX)       11-11         Figure 11-10. PWM Data Register (PWMEX)       11-11         Figure 12-2. A/D Converter Control Register (ADCON)       12-2         Figure 12-3. A/D Converter Control Register (ADCON)       12-2         Figure 13-4. Flash Memory Sector Address Register (FMUSR)       13-2         Figure 13-4. Flash Memory Sector Address Register (FMUSR)                                                      | Figure 10-1. Basic Timer Control Register (BTCON)                            |       |

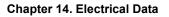

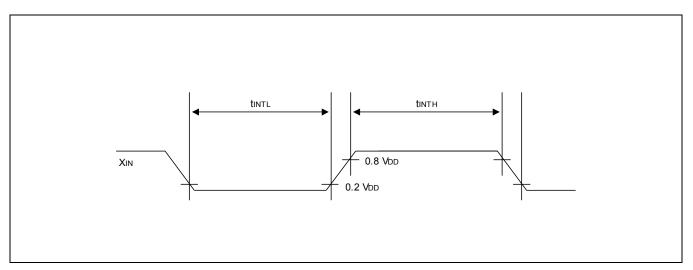

| Figure 10-4. Timer 0 Control Registers (TOCON).10-7Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode).10-8Figure 10-6. Timer 0 Timing Diagram.10-9Figure 10-7. Basic Timer and Timer 0 Block Diagram.10-10Figure 11-1. PWM Data and Extension Registers.11-2Figure 11-2. PWM Basic Waveform (6-bit base).11-4Figure 11-3. Extended PWM Waveform (6-bit base + 2-bit extension).11-5Figure 11-4. PWM Basic Waveform (6-bit base).11-6Figure 11-5. Extended PWM Waveform (6-bit base).11-6Figure 11-6. PWM Basic Waveform (6-bit base).11-7Figure 11-7. PWM Extension Register (PWMCN).11-10Figure 11-8. PWM Control Register (PWMCN).11-11Figure 11-9. PWM Extension Register (PWMEX).11-11Figure 11-10. PWM Data Register (PWMDATA).11-11Figure 11-12. PWM Module Functional Block Diagram.11-2Figure 12-1. A/D Converter Control Register (ADCON).12-2Figure 12-3. A/D Converter Circuit Diagram.12-3Figure 12-4. A/D Converter Data Register (ADCAN+//L).12-3Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy.12-2Figure 13-1. Flash Memory Sector Address Register (FMSECL).13-3Figure 13-3. Flash Memory Sector Address Register (FMSECL).13-4Figure 13-4. Sector Erase Flowchart in a User Program Mode.13-6Figure 13-5. Sector Configurations in User Program Mode.13-6Figure 13-6. Sector Erase Flowchart in a User Program Mode.13-6Figure 14-1. Input Timing Measurement Poin                | Figure 10-2. Oscillation Stabilization Time on RESET                         |       |

| Figure 10-4. Timer 0 Control Registers (TOCON).10-7Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode).10-8Figure 10-6. Timer 0 Timing Diagram.10-9Figure 10-7. Basic Timer and Timer 0 Block Diagram.10-10Figure 11-1. PWM Data and Extension Registers.11-2Figure 11-2. PWM Basic Waveform (6-bit base).11-4Figure 11-3. Extended PWM Waveform (6-bit base + 2-bit extension).11-5Figure 11-4. PWM Basic Waveform (6-bit base).11-6Figure 11-5. Extended PWM Waveform (6-bit base).11-6Figure 11-6. PWM Basic Waveform (6-bit base).11-7Figure 11-7. PWM Extension Register (PWMCN).11-10Figure 11-8. PWM Control Register (PWMCN).11-11Figure 11-9. PWM Extension Register (PWMEX).11-11Figure 11-10. PWM Data Register (PWMDATA).11-11Figure 11-12. PWM Module Functional Block Diagram.11-2Figure 12-1. A/D Converter Control Register (ADCON).12-2Figure 12-3. A/D Converter Circuit Diagram.12-3Figure 12-4. A/D Converter Data Register (ADCAN+//L).12-3Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy.12-2Figure 13-1. Flash Memory Sector Address Register (FMSECL).13-3Figure 13-3. Flash Memory Sector Address Register (FMSECL).13-4Figure 13-4. Sector Erase Flowchart in a User Program Mode.13-6Figure 13-5. Sector Configurations in User Program Mode.13-6Figure 13-6. Sector Erase Flowchart in a User Program Mode.13-6Figure 14-1. Input Timing Measurement Poin                | Figure 10-3. Oscillation Stabilization Time on Stop Mode Release             |       |

| Figure 10-6. Timer 0 Timing Diagram.10-9Figure 10-7. Basic Timer and Timer 0 Block Diagram.10-10Figure 11-1. PWM Data and Extension Registers.11-2Figure 11-2. PWM Basic Waveform (6-bit base).11+4Figure 11-3. Extended PWM Waveform (6-bit base).11-5Figure 11-4. PWM Basic Waveform (6-bit base).11-6Figure 11-5. Extended PWM Waveform (6-bit base).11-7Figure 11-6. Extended PWM Waveform (6-bit base).11-7Figure 11-6. Extended PWM Waveform (6-bit base).11-7Figure 11-6. PWM Basic Waveform (8-bit base).11-16Figure 11-6. PWM Basic Waveform (8-bit base).11-11Figure 11-7. PWM Extension Register (PWMCON).11-11Figure 11-8. PWM Control Register (PWMEX).11-11Figure 11-9. PWM Data Register (PWMEX).11-11Figure 11-10. PWM Data Register (PWMDATA).11-11Figure 11-12. PWM Module Functional Block Diagram.11-22Figure 12-1. A/D Converter Control Register (ADCON).12-23Figure 12-2. A/D Converter Control Register (ADCON).12-23Figure 12-3. A/D Converter Control Register (FMCON).12-25Figure 13-1. Flash Memory Control Register (FMCON).13-26Figure 13-2. Flash Memory Sector Address Register (FMSECH).13-34Figure 13-3. Flash Memory Sector Address Register (FMSECH).13-34Figure 13-4. Flash Memory Sector Address Register (FMSECH).13-44Figure 13-5. Sector Configurations in User Program Mode.13-56Figure 13-6. Sector Erase Flowchart in a User Program Mode.13-56Figure 13-7. Byt                                           |                                                                              |       |

| Figure 10-7. Basic Timer and Timer 0 Block Diagram.       10-10         Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-2. PWM Basic Waveform (6-bit base)       11-4         Figure 11-3. Extended PWM Waveform (6-bit base)       11-5         Figure 11-4. PWM Basic Waveform (6-bit base)       11-6         Figure 11-5. Extended PWM Waveform (6-bit base)       11-6         Figure 11-6. PWM Basic Waveform (6-bit base)       11-7         Figure 11-6. PWM Basic Waveform (6-bit base)       11-7         Figure 11-8. Extended PWM Waveform (6-bit base)       11-8         Figure 11-8. PWM Control Register (PWMCON)       11-10         Figure 11-9. PWM Extension Register (PWMCAN)       11-11         Figure 11-12. PWM Module Functional Block Diagram       11-12         Figure 12-1. A/D Converter Control Register (ADCON)       12-2         Figure 12-3. A/D Converter Control Register (ADDATAH/L)       12-3         Figure 12-4. A/D Converter Timing Diagram       12-4         Figure 13-2. Flash Memory User Programming Enable Register (FMUSR)       13-2         Figure 13-3. Flash Memory User Programming Enable Register (FMUSR)       13-3         Figure 13-4. Flash Memory Sector Address Register (FMSECL)       13-4         Figure 13-5. Sector Configurations in User Program Mode       13-6         Figure 13-6. Sector Erase                                                 | Figure 10-5. Simplified Timer 0 Function Diagram (Interval Timer Mode)       |       |

| Figure 11-1. PWM Data and Extension Registers       11-2         Figure 11-2. PWM Basic Waveform (6-bit base)       11-4         Figure 11-3. Extended PWM Waveform (6-bit base + 2-bit extension)       11-5         Figure 11-5. Extended PWM Waveform (6-bit base + 6-bit extension)       11-7         Figure 11-6. PWM Basic Waveform (8-bit base)       11-8         Figure 11-6. PWM Basic Waveform (8-bit base)       11-7         Figure 11-8. PWM Control Register (PWMCON)       11-10         Figure 11-9. PWM Extension Register (PWMDATA)       11-11         Figure 11-10. PWM Data Register (PWMDATA)       11-11         Figure 12-1. A/D Converter Control Register (ADCON)       12-2         Figure 12-2. A/D Converter Control Register (ADDATAH/L)       12-3         Figure 12-3. A/D Converter Data Register (ADDATAH/L)       12-3         Figure 12-4. A/D Converter Diagram       12-3         Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy       12-5         Figure 13-1. Flash Memory Sector Address Register (FMSECH)       13-4         Figure 13-3. Flash Memory Sector Address Register (FMSECH)       13-4         Figure 13-4. Flash Memory Sector Address Register (FMSECH)       13-4         Figure 13-5. Sector Configurations in User Program Mode       13-5         Figure 13-6. Sector Configurations in User Program Mode       13-9                                     | Figure 10-6. Timer 0 Timing Diagram                                          |       |

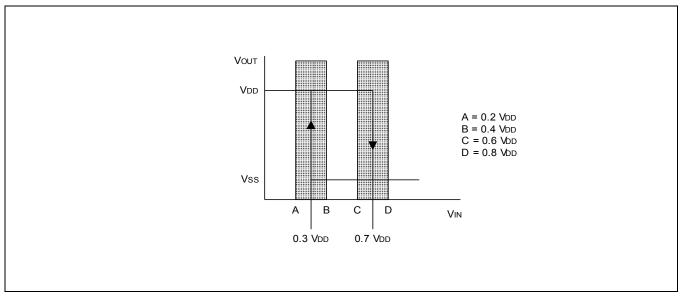

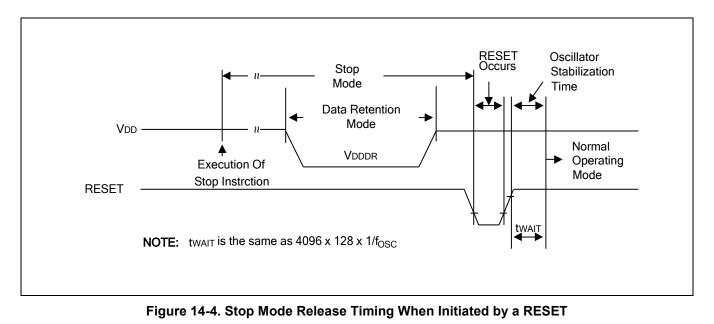

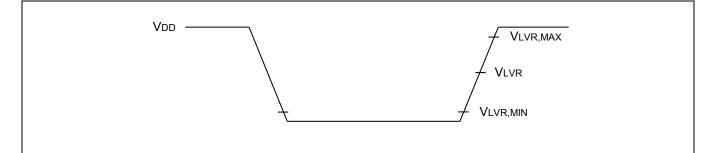

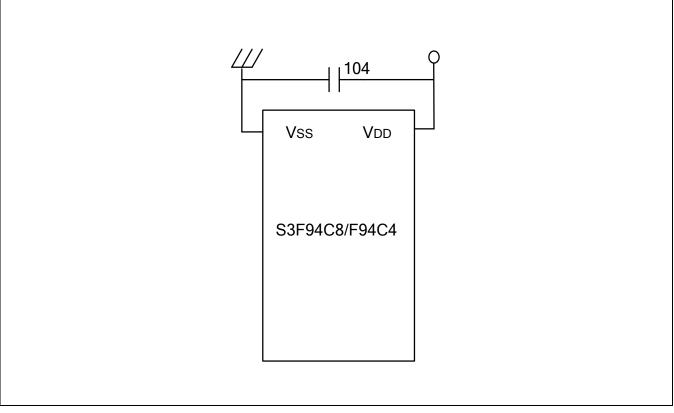

| F\u00ed_url11-2PWM Basic Waveform (6-bit Dase)11-4Figure 11-3. Extended PWM Waveform (6-bit base)11-5Figure 11-4. PWM Basic Waveform (6-bit base)11-6Figure 11-5. Extended PWM Waveform (6-bit base)11-7Figure 11-6. PWM Basic Waveform (8-bit base)11-7Figure 11-7. PWM Basic Waveform (8-bit base)11-7Figure 11-8. PWM Control Register (PWMCON)11-10Figure 11-9. PWM Extension Register (PWMEX)11-11Figure 11-10. PWM Data Register (PWMDATA)11-11Figure 11-12. PWM Module Functional Block Diagram11-22Figure 12-1. A/D Converter Control Register (ADCON)12-2Figure 12-2. A/D Converter Control Register (ADCAN)12-3Figure 12-3. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-4. A/D Converter Timing Diagram12-4Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory Sector Address Register (FMSECL)13-3Figure 13-3. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-6. Sector Configurations in User Program Mode13-5Figure 13-7. Byte Program Flowchart in a User Program Mode13-9Figure 13-8. Program Flowchart in a User Program Mode13-9Figure 13-8. Program Flowchart in a User Program Mode13-9Figure 14-1. Input Timing Measurement Points.14-5Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a                                   | Figure 10-7. Basic Timer and Timer 0 Block Diagram                           | 10-10 |

| Figure 11-3. Extended PWM Waveform (6-bit base + 2-bit extension)11-5Figure 11-4. PWM Basic Waveform (6-bit base)11-6Figure 11-5. Extended PWM Waveform (8-bit base + 6-bit extension)11-7Figure 11-6. PWM Basic Waveform (8-bit base)11-8Figure 11-8. PWM Control Register (PWMCON)11-10Figure 11-9. PWM Extension Register (PWMCAN)11-11Figure 11-10. PWM Data Register (PWMDATA)11-11Figure 11-12. PWM Module Functional Block Diagram11-22Figure 12-1. A/D Converter Control Register (ADCON)12-2Figure 12-2. A/D Converter Control Register (ADDATAH/L)12-3Figure 12-3. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-4. A/D Converter Tata Register (ADDATAH/L)12-3Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory Sector Address Register (FMSECH)13-4Figure 13-5. Sector Configurations in User Program Mode13-4Figure 13-6. Sector Configurations in User Program Mode13-6Figure 13-7. Byte Program Flowchart in a User Program Mode13-10Figure 14-8. Program Flowchart in a User Program Mode13-10Figure 14-9. Contract in Suster Program Mode13-10Figure 14-9. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-1. Input Timing Measurement Points14-48Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-9Fi                | Figure 11-1. PWM Data and Extension Registers                                |       |

| Figure 11-4. PWM Basic Waveform (6-bit base)11-6Figure 11-5. Extended PVM Waveform (6-bit base + 6-bit extension)11-7Figure 11-6. PWM Basic Waveform (8-bit base)11-8Figure 11-6. PWM Easic Waveform (8-bit base)11-8Figure 11-8. PWM Control Register (PWMCON)11-10Figure 11-9. PWM Extension Register (PWMEX)11-11Figure 11-10. PWM Data Register (PWMEX)11-11Figure 11-10. PWM Data Register (PWMDATA)11-11Figure 11-12. PWM Module Functional Block Diagram11-22Figure 12-2. A/D Converter Control Register (ADCON)12-23Figure 12-3. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-4. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-2. Flash Memory Control Register (FMCON)13-2Figure 13-3. Flash Memory Sector Address Register (FMSECH)13-3Figure 13-4. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-5. Sector Configurations in User Program Mode13-5Figure 13-6. Sector Erase Flowchart in User Program Mode13-5Figure 13-7. Byte Program Flowchart in a User Program Mode13-9Figure 14-2. Operating Voltage Range14-8Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-9Figure 14-5. LVR Reset Timing14-11Figure 14-5. LVR Reset Timing14-11Figure 14-5. LVR Reset Timing14-11Figure 14-5. LVR Reset Ti                                           | Figure 11-2. PWM Basic Waveform (6-bit base)                                 | 11-4  |

| Figure 11-5. Extended PWM Waveform (6-bit base + 6-bit extension)11-7Figure 11-6. PWM Basic Waveform (8-bit base)11-8Figure 11-8. PWM Control Register (PWMCON)11-10Figure 11-9. PWM Extension Register (PWMEX)11-11Figure 11-10. PWM Data Register (PWMDATA)11-11Figure 11-12. PWM Module Functional Block Diagram11-12Figure 12-1. A/D Converter Control Register (ADCON)12-2Figure 12-2. A/D Converter Circuit Diagram12-3Figure 12-3. A/D Converter Circuit Diagram12-3Figure 12-4. A/D Converter Timing Diagram12-3Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-7. Flash Memory Control Register (FMCON)13-2Figure 13-8. Flash Memory Sector Address Register (FMSECH)13-4Figure 13-7. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-7. Byte Program Flowchart in a User Program Mode13-6Figure 13-7. Byte Program Flowchart in a User Program Mode13-10Figure 14-1. Input Timing Measurement Points14-5Figure 14-2. Operating Voltage Range14-8Figure 14-3. Schwitt Trigger Input Characteristics Diagram14-14Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-12Figure 14-5. LVR Reset Timing14-14Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-12Figure 14-5. LVR Reset Timing14-11Figure 14-5. LVR Reset Timing14-12Figure 15-1. 20-DIP-300A Package Dimensions15-1Figure 15-2. USOP-375 Package Di                                           | Figure 11-3. Extended PWM Waveform (6-bit base + 2-bit extension)            | 11-5  |

| Figure 11-6. PWM Basic Waveform (8-bit base)11-8Figure 11-8. PWM Control Register (PWMCON)11-10Figure 11-8. PWM Extension Register (PWMEX)11-11Figure 11-10. PWM Data Register (PWMDATA)11-11Figure 11-12. PWM Module Functional Block Diagram11-12Figure 12-1. A/D Converter Control Register (ADCON)12-2Figure 12-2. A/D Converter Circuit Diagram12-3Figure 12-3. A/D Converter Circuit Diagram12-3Figure 12-4. A/D Converter Timing Diagram12-3Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory Sector Address Register (FMUSR)13-3Figure 13-3. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-4. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-5. Sector Configurations in User Program Mode13-6Figure 13-7. Byte Program Flowchart in a User Program Mode13-6Figure 13-8. Program Flowchart in a User Program Mode13-10Figure 14-1. Input Timing Measurement Points14-5Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing14-11Figure 14-5. LVR Reset Timing14-11Figure 14-6. The Circuit Diagram to Improve EFT Characteristics14-11Figure 15-1. 20-DIP-300A Package Dimensions15-1Figure 15-2. OSCP-375 Package Dimensions15-1                                                                                                                        | Figure 11-4. PWM Basic Waveform (6-bit base)                                 |       |

| Figure 11-8. PWM Control Register (PWMCON)11-10Figure 11-9. PWM Extension Register (PWMEX)11-11Figure 11-9. PWM Data Register (PWMDATA)11-11Figure 11-10. PWM Module Functional Block Diagram11-11Figure 12-1. A/D Converter Control Register (ADCON)12-2Figure 12-2. A/D Converter Circuit Diagram12-3Figure 12-3. A/D Converter Timing Diagram12-3Figure 12-4. A/D Converter Timing Diagram12-4Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-6. Flash Memory Control Register (FMCON)13-2Figure 13-7. Flash Memory Sector Address Register (FMSECH)13-4Figure 13-8. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-7. Sector Configurations in User Program Mode13-5Figure 13-7. Byte Program Flowchart in User Program Mode13-9Figure 13-8. Program Flowchart in a User Program Mode13-9Figure 13-8. Program Flowchart in a User Program Mode13-10Figure 14-1. Input Timing Measurement Points14-5Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing Wen Initiated by a RESET14-9Figure 14-5. LVR Reset Timing14-11Figure 14-6. The Circuit Diagram to Improve EFT Characteristics14-11Figure 15-1. 20-DIP-300A Package Dimensions15-1Figure 15-2. OSOP-375 Package Dimensions15-1                                                                                                                                                        |                                                                              |       |

| Figure 11-9. PWM Extension Register (PWMEX)11-11Figure 11-10. PWM Data Register (PWMDATA)11-11Figure 11-12. PWM Module Functional Block Diagram11-12Figure 12-1. A/D Converter Control Register (ADCON)12-2Figure 12-2. A/D Converter Circuit Diagram12-3Figure 12-3. A/D Converter Circuit Diagram12-3Figure 12-4. A/D Converter Timing Diagram12-3Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory User Programming Enable Register (FMUSR)13-3Figure 13-3. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-6. Sector Configurations in User Program Mode13-5Figure 13-7. Byte Program Flowchart in a User Program Mode13-9Figure 13-8. Program Flowchart in a User Program Mode13-10Figure 14-1. Input Timing Measurement Points14-5Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-9Figure 14-5. LVR Reset Timing14-11Figure 14-6. The Circuit Diagram to Improve EFT Characteristics14-11Figure 15-1. 20-DIP-300A Package Dimensions15-2                                                                                                                                                                                                                                                                                               | Figure 11-6. PWM Basic Waveform (8-bit base)                                 | 11-8  |

| Figure 11-10. PWM Data Register (PWMDATA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |       |

| Figure 11-12.PWM Module Functional Block Diagram11-12Figure 12-1. A/D Converter Control Register (ADCON)12-2Figure 12-2. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-3. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-4. A/D Converter Timing Diagram12-4Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory User Programming Enable Register (FMUSR)13-3Figure 13-3. Flash Memory Sector Address Register (FMSECH)13-4Figure 13-4. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-5. Sector Configurations in User Program Mode13-5Figure 13-7. Byte Program Flowchart in a User Program Mode13-6Figure 13-8. Program Flowchart in a User Program Mode13-9Figure 14-1. Input Timing Measurement Points14-5Figure 14-2. Operating Voltage Range14-8Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-9Figure 14-5. LVR Reset Timing14-11Figure 15-1. 20-DIP-300A Package Dimensions15-1Figure 15-2. 20-SOP-375 Package Dimensions15-2                                                                                                                                                                                                                                                                                           |                                                                              |       |

| Figure 12-1. A/D Converter Control Register (ADCON)       12-2         Figure 12-2. A/D Converter Circuit Diagram       12-3         Figure 12-3. A/D Converter Data Register (ADDATAH/L)       12-3         Figure 12-4. A/D Converter Timing Diagram       12-4         Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy       12-5         Figure 13-1. Flash Memory Control Register (FMCON)       13-2         Figure 13-2. Flash Memory User Programming Enable Register (FMUSR)       13-3         Figure 13-3. Flash Memory Sector Address Register (FMSECH)       13-4         Figure 13-4. Flash Memory Sector Address Register (FMSECL)       13-4         Figure 13-5. Sector Configurations in User Program Mode       13-5         Figure 13-6. Sector Erase Flowchart in User Program Mode       13-9         Figure 13-7. Byte Program Flowchart in a User Program Mode       13-9         Figure 13-8. Program Flowchart in a User Program Mode       13-10         Figure 14-1. Input Timing Measurement Points       14-5         Figure 14-2. Operating Voltage Range       14-8         Figure 14-3. Schmitt Trigger Input Characteristics Diagram       14-8         Figure 14-4. Stop Mode Release Timing When Initiated by a RESET       14-9         Figure 14-4. Stop Mode Release Timing When Initiated by a RESET       14-11         Figure 15-1. 20-DIP-300A Package Dimensions             |                                                                              |       |

| Figure 12-2. A/D Converter Circuit Diagram12-3Figure 12-3. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-4. A/D Converter Timing Diagram12-4Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory User Programming Enable Register (FMUSR)13-3Figure 13-3. Flash Memory Sector Address Register (FMSECH)13-4Figure 13-4. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-5. Sector Configurations in User Program Mode13-5Figure 13-6. Sector Erase Flowchart in User Program Mode13-6Figure 13-7. Byte Program Flowchart in a User Program Mode13-9Figure 14-1. Input Timing Measurement Points14-5Figure 14-2. Operating Voltage Range14-8Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-9Figure 15-1. 20-DIP-300A Package Dimensions15-1Figure 15-2. 20-SOP-375 Package Dimensions15-2                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 11-12. PWM Module Functional Block Diagram                            | 11-12 |

| Figure 12-3. A/D Converter Data Register (ADDATAH/L)12-3Figure 12-4. A/D Converter Timing Diagram12-4Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory User Programming Enable Register (FMUSR)13-3Figure 13-3. Flash Memory Sector Address Register (FMSECH)13-4Figure 13-4. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-5. Sector Configurations in User Program Mode13-5Figure 13-6. Sector Erase Flowchart in User Program Mode13-6Figure 13-7. Byte Program Flowchart in a User Program Mode13-9Figure 14-1. Input Timing Measurement Points.14-5Figure 14-2. Operating Voltage Range14-8Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-9Figure 15-1. 20-DIP-300A Package Dimensions15-1Figure 15-2. 20-SOP-375 Package Dimensions15-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |       |

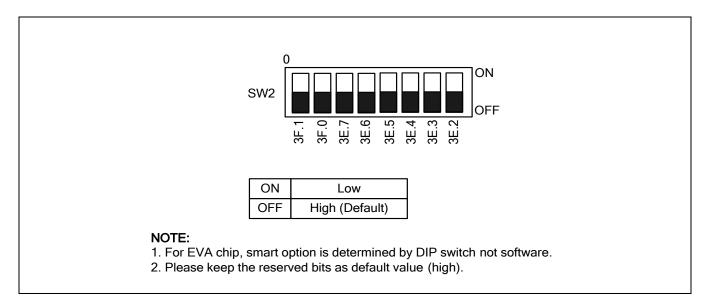

| Figure 12-4. A/D Converter Timing Diagram12-4Figure 12-5. Recommended A/D Converter Circuit for Highest Absolute Accuracy12-5Figure 13-1. Flash Memory Control Register (FMCON)13-2Figure 13-2. Flash Memory User Programming Enable Register (FMUSR)13-3Figure 13-3. Flash Memory Sector Address Register (FMSECH)13-4Figure 13-4. Flash Memory Sector Address Register (FMSECL)13-4Figure 13-5. Sector Configurations in User Program Mode13-5Figure 13-6. Sector Erase Flowchart in User Program Mode13-6Figure 13-7. Byte Program Flowchart in a User Program Mode13-9Figure 14-8. Program Flowchart in a User Program Mode13-10Figure 14-1. Input Timing Measurement Points14-5Figure 14-2. Operating Voltage Range14-8Figure 14-3. Schmitt Trigger Input Characteristics Diagram14-8Figure 14-4. Stop Mode Release Timing When Initiated by a RESET14-9Figure 14-5. LVR Reset Timing14-11Figure 15-1. 20-DIP-300A Package Dimensions15-1Figure 15-2. 20-SOP-375 Package Dimensions15-2                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              |       |